Intel Agilex: 10nm FPGAs with PCIe 5.0, DDR5, and CXL

by Ian Cutress on April 2, 2019 1:00 PM EST

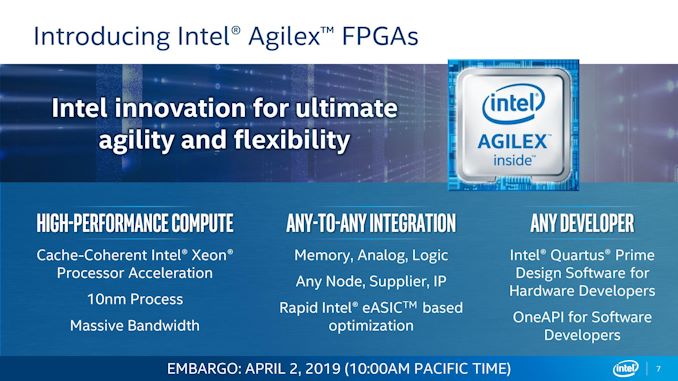

Ever since Intel purchased Altera for an enormous amount of money a few years ago (ed: $16.7B), the FPGA portfolio that has been coming out has largely been a product of the pre-Intel days. Today however that changes, as Intel is announcing its first fully Intel-designed FPGA, built upon its own internal 10nm process, with the Agilex brand name. This new range of products is set to roll out later this year for sampling, and offer a mix of analog, digital, memory, custom IO, and eASIC variations within a singular platform.

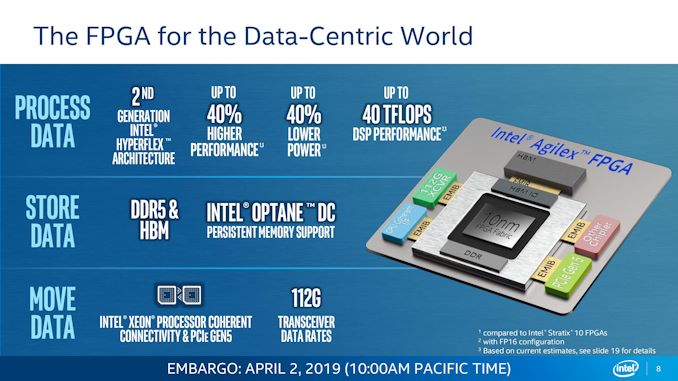

For users familiar with Intel’s FPGA family, the new Agilex portfolio is a generational upgrade over the current Stratix 10 family. The new Agilex parts, according to Intel, offer up to 40% higher performance or 40% lower power, up to 40 TFLOPs of DSP performance, and support for all the latest and future technologies. It’s this latter part that becomes important as the role of the FPGA is transmogrifying into a general purpose design platform into an optimized compute platform.

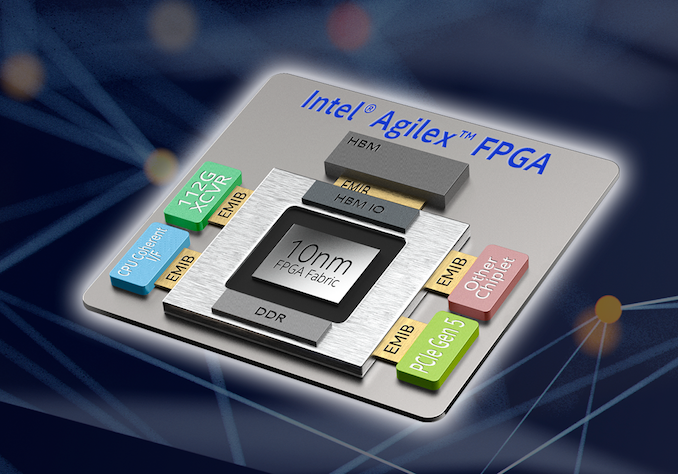

The Agilex FPGA builds on similar design principles to the Stratix – a centralized FPGA block of gates with hardened features and external connections out to several different technologies, based on the customer requirements. For these external connections, Intel is using its Embedded Multi-Die Interconnect Bridge (EMIB) technology, which in the examples given can be expanded into other chiplets. Some of the chiplet suggestions from Intel include High Bandwidth Memory (HBM), next-generation 112G transceivers, PCIe Gen 5.0 root complexes, Compute eXpress Link interfaces (through PCIe 5.0), additional CPU cache coherent interconnects, and other chiplets/IP as determined by the customer. To add into all of this, Agilex will also support Intel’s Optane DC Persistent Memory.

One of the big updates to the FPGA family comes through Intel’s recent acquisition of eASIC. Intel has actually been working with eASIC for several years, however in 2018 it purchased the company outright to deliver additional synergies into its programmable product portfolio. With Agilex, the first stage of this vision is set to be delivered – customers that want quick IP deployment can choose to work with Intel’s eASIC division for chiplet IP deployment or fusion into the FPGA, quicker than the customer is able to do themselves, and taking advantage of Intel’s own product design chain.

The use of PCIe Gen 5.0 is also a big element to Agilex, as it allows customers to connect directly with future PCIe 5.0 host devices, but it also allows for Intel’s new Compute eXpress Link technology, which builds upon the PCIe 5.0 physical standards. CXL is Intel’s own cache coherent connect, set to work alongside (or compete, depending on who you ask) with GenZ and CCIX. Given Intel’s comments on CXL, it’s clear that when PCIe 5.0 is ubiquitous, it intends to bring its add-in card portfolio to run either on CXL, PCIe 5.0, or both. And one of Intel’s big topics recently is its movement into discrete graphics, which could take advantage of this. It would appear however that Agilex may be the first to take advantage of Intel’s new standard when it’s ready – until that point, Intel states that Agilex will support UPI as its main cache coherent connectivity option.

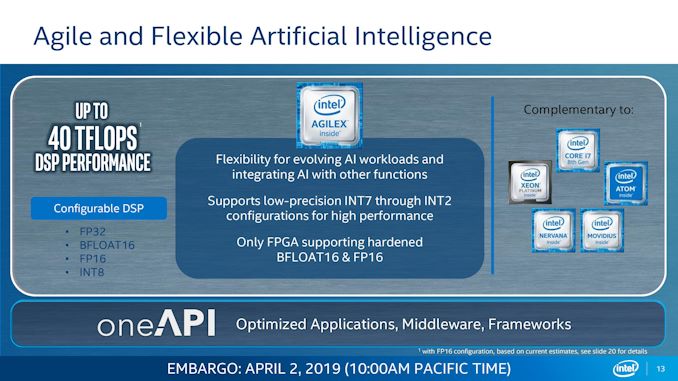

As always with the FPGA market, Intel is targeting the usual suspects that might use them: networking, cloud, embedded, and enterprise. The newest use cases for FPGAs in this field are related to edge deployments as well as networking, so we can expect to see Intel’s case studies of the new hardware in these areas. AI is also important, with Intel keen to announce that its Agilex portfolio will have hardened support for bfloat16 and other low precision number formats, even down to INT2. These will be managed through Intel’s OneAPI strategy, and the company states that even though the FPGA can be used for AI, it is set to work alongside Nirvana and Movidius, rather than compete.

One element that was interesting during our discussions with Intel about Agilex is that the company mentioned 3D stacking and integration. I quizzed if this was just a mentioning of HBM, or something more detailed such as the Foveros technology that the company demonstrated at the end of 2018. Intel stated that the 3D integration is going to be an expected evolution of the product line, and a view to the future with its second generation of Agilex. Perhaps expected, no date about when this would happen was forthcoming, but interesting nonetheless.

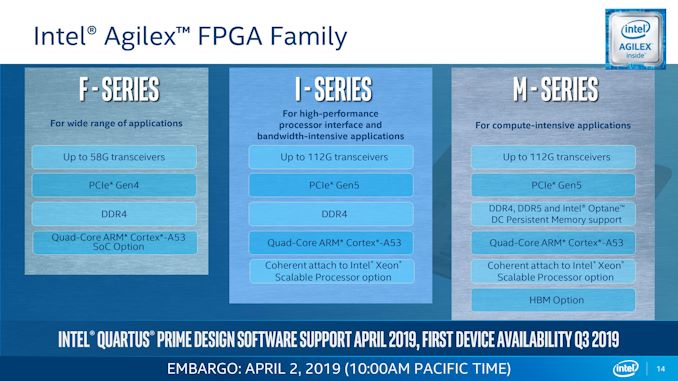

Agilex will come in three flavors: F, I, and M, with exact support listed below. The Intel Quartus Prime software will support these variants from April 2019, and first device availability of the F-series will be from Q3 2019.

Related Reading

- Intel Announces The FPGA PAC N3000 for 5G Networks

- Intel To Acquire eASIC: Lower Cost ASICs in FPGA Design Time

- Intel Shows Xeon Scalable Gold 6138P with Integrated FPGA, Shipping to Vendors

- Xilinx Announces Project Everest: The 7nm FPGA SoC Hybrid

- Xilinx Announce New RFSoCs for 5G, Covering Sub-6 GHz and mmWave

- Intel to Acquire FPGA-Specialist Altera for $16.7 Billion

11 Comments

View All Comments

jamesindevon - Tuesday, April 2, 2019 - link

How credible is any Intel announcement of 10nm chips? Who's going to risk a product line on them without serious market development cash?hpglow - Tuesday, April 2, 2019 - link

Right now it will only be Intel trusting this. The article doesn't state that the chiplets on the interposer have to be 10nm. Also Intel put a much more competent team on building out 7nm. Possibly these issues will be resolved on that node as they are not going to be relying on multi patterning as much on that node.ksec - Tuesday, April 2, 2019 - link

These 10nm are from the ( old? ) Custom Foundry, Intel mentioned the 10nm used in Custom Foundry is different to 10nm used in to their CPU, which has different set of design rules compares to 10nm used in Desktop / Server and Mobile.HStewart - Wednesday, April 3, 2019 - link

So this means this chip does not have designed issues in Cannon Lake.FreckledTrout - Tuesday, April 2, 2019 - link

Likely very credible. The chiplet design allows for using different process for the various chiplets much like AMD is using 14nm for the IO and 7nm for the CPu chiplet in the upcoming Zen2.HStewart - Wednesday, April 3, 2019 - link

I would agree it creditable, but this designed is already out with DELL XPS 15 2in1. Big question does the AMD designed allow non AMD components. I would think this flexibility is important where Intel is aiming this product at.Valantar - Wednesday, April 3, 2019 - link

You're confusing EMIB with 10nm process tech - two entirely different things. Nobody is questioning Intel's ability to link together chiplets with EMIB, just their ability to make chips on 10nm.As someone said above, though, this is (reportedly) a different 10nm process from the defective CPU process, and besides that FPGAs are by their programmable nature more fault-tolerant than fixed-function hardware (just disable any damaged gates/etc., program around the error).

HStewart - Wednesday, April 3, 2019 - link

I think one needs to first look at this market, Altera was pretty much the leader of market - plus these are specialize products and perfect platform for Intel to test new process. In fact remember that EMiB is involved - I am typing this on a notebook (DELL XPS 15 2in1) that has EMiB on it with non Intel ( AMD) GPU - So 10nm on this device might be just FPGAI think it getting old for people blaming 10nm issues on Intel.This is likely not the same 10nm version that is used in Cannon Lake but something closer to Ice Lake that is coming out later this years.

Yorgos - Sunday, April 7, 2019 - link

that's why intel has purch and other companies to advertise their products.Intel doesn't have a 5g modem, but pays to get press attention for it.

Intel doesn't have a 10nm chip, but pays the press to "review" some samples

Altera has been shrinking since they got acpuired by intel, but hey just hit the meme button and put DDR5, 10nm, PCIe-5.0 in one article as bait for the clueless.

I don't regret at all, in fact I am more than happy everyday that I was lucky to work on the Xilinx eco-system for over 6 years.

Back in the day altera was pretty competitive, they came and showed us the first, unreleased back in 2013, opecl sdk with goodies like matlab integration... but after that, nothing.

disclaimer: Altera/Intel PSG or whatever they call it the kids nowadays, isn't just an fpga company anymore. Their numbers are inflated by adding "5g" tranceivers, embedded boards that intel will kill off in a few quarters and a ton(SI) of other devices that altera never made or intended to make. So, yeah, those numbrers on YoY growth are not only for fpgas, they contain Altera + intel's embedded division sales. Also note that intel killed the support for the "V" line of fpgas due to *Customer demand declined and continued support for these devices is no longer viable* as they put it exactly in their announcement. Guess what! devices with Spartan III are STILL made. head over to ettus and grab those sweet mini usrps. Since I work in r&d and have close ties with many uni research groups, everyone is developing on Xilinx. Even the freshly "opensourced" MIPS designs where sent to research groups were paired with ultrascale fpgas... in fact there are several on the next room where 2-3 phds are working on them.

to conclude, advertorials have zero credibility, they are just ads.

YB1064 - Monday, April 8, 2019 - link

As long as Xilinx have a powerhouse like National Instruments in their corner, no other FPGA maker can come close to sniffing the edu/research user space. Intel have a horrific track record supporting their ucontrollers. The Quark was a buggy, putrid mess.