Spotted At Hot Chips: Quad Tile Intel Xe-HP GPU

by Ryan Smith on August 17, 2020 7:00 PM EST- Posted in

- GPUs

- Intel

- Xe-HP

- Hot Chips 32

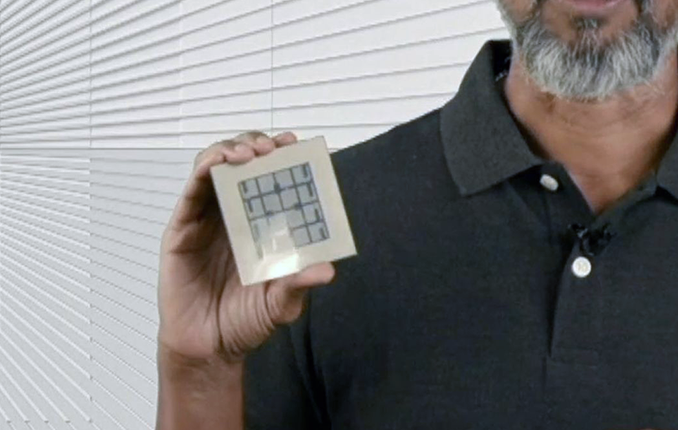

At last week’s Intel Architecture Day, Intel’s chief architect, Raja Koduri, briefly held up the smallest member of the company’s forthcoming Xe-HP series of server CPUs, the one tile configuration. Now, only a few days later, he has upped the ante by showing off the largest, four tile configuration.

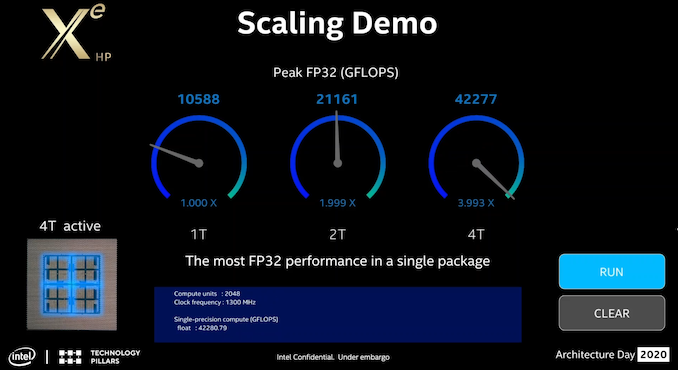

Designed to be a scalable chip architecture, Xe-HP is set to be available with one, two, or four tiles. And while Intel has yet to disclose too much in the way of details on the architecture, based on their packaging disclosures it looks like the company is using their EMIB tech to wire up the GPU tiles, as well as the GPU’s on-package HBM memory.

Assuming it makes it to market, a multi-tiled GPU – essentially multiple GPUs in a single package – would be a major accomplishment for Intel. GPUs are notoriously bandwidth-hungry due to the need to shovel data around between cores, caches, and command frontends, which makes them non-trivial to split up in a chiplet/tiled fashion. Even if Intel can only use this kind of multi-tile scalability for compute workloads, that would have a significant impact on what kind of performance a single GPU package can attain, and how future servers might be built.

27 Comments

View All Comments

austinsguitar - Monday, August 17, 2020 - link

:) nice glued together gpus.shabby - Monday, August 17, 2020 - link

Almost looks like pl adhesive...CajunArson - Monday, August 17, 2020 - link

If you want to call the advanced 2D & 3D packaging that Intel is using "glue" then Lisa Su would gladly kill your dog if it meant she could sniff it.close - Tuesday, August 18, 2020 - link

That's actually Intel's official terminology for AMD's EPYC "glued together" CPU in the past. So why call this "advanced 2D & 3D packaging" when these are just glued together GPUs? Comments? Questions? ;)https://www.techpowerup.com/235092/intel-says-amd-...

edzieba - Tuesday, August 18, 2020 - link

Because of the difference between through-substrate interconnects and through-silicon interconnects (EMIB, or whole-package interposer, or stacked TSV) in power, bandwidth, and latency (redrivers ain't free y'know).Intel's 'glue' comment stemmed from AMD's use of the same term for the dual-die Pentium D.

yeeeeman - Tuesday, August 18, 2020 - link

Exactly. How AMD fanboys forget that AMD also had its irony moments...But nowadays, only Intel is making mistakes and AMD is perfection.

deil - Tuesday, August 18, 2020 - link

Context is needed. You expect more from someone who was leader for 10+ years without any competition. Also AMD for someone that was unable to pull its pants up for so long, this is incredible progress. they like, switched places within 5 years?Flunk - Tuesday, August 18, 2020 - link

Just because AMD has said stupid things, doesn't mean you can't call out Intel for saying stupid things. And not everyone who speaks out against Intel is autmatically a fan of their #1 competitor.close - Tuesday, August 18, 2020 - link

@yeeeeman, "But nowadays, only Intel is making mistakes and AMD is perfection." Pretty accurate although AMD is also far from perfection. This being said let's hold the whining until the roles switch again.dullard - Tuesday, August 18, 2020 - link

Exactly. Intel was ridiculed by AMD and AMD supporters for years for "gluing". Then, suddenly one internal slide on one presentation from Intel joked back about AMD "gluing" and it is now Intel's fault for using the term. Why can't people understand the context?