Intel Alder Lake: Confirmed x86 Hybrid with Golden Cove and Gracemont for 2021

by Dr. Ian Cutress on August 14, 2020 1:05 PM EST- Posted in

- CPUs

- Intel

- Alder Lake

- Hybrid

- Intel Arch Day 2020

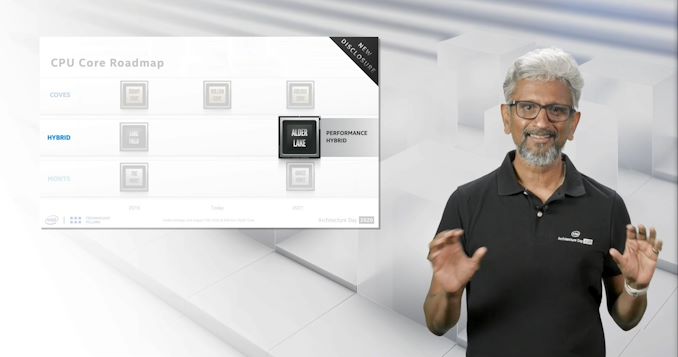

Following leaks is often a game of cat and mouse – what is actually legitimate and what might not be. Traditionally AnandTech shies away from leaks for that very reason, and we prefer to have multiple sources that are saying the same thing, rather than addressing every potential rumor on the blogosphere. Nonetheless, hints towards a new product from Intel, Alder Lake, have been cropping up over the past few months, including getting a small mention in Intel’s Q2 2020 earnings. The leaks have suggested that it would offer a mixed Hybrid x86 environment similar to Intel’s current Lakefield product that uses high-performance cores paired with high-efficiency cores. As part of Intel’s Architecture Day 2020, the company officially announced Alder Lake as a hybrid x86 product on its roadmaps.

In the roadmap and as part of the discussions, Intel’s Raja Koduri confirms that Alder Lake will be a combination of the Golden Cove high performance computing core and the Gracemont high efficiency core, and the goal of this chip is to offer a ‘Performance Hybrid’ option into the portfolio. Raja explained to the audience that the company has learned a lot due to building Lakefield, its current hybrid x86 chip for thin and light notebooks, and while Lakefield was focused on battery life, Alder Lake will focus instead on performance.

Alder Lake will involve Intel’s next generation hardware scheduler, which we are told will be able to leverage all cores for performance and make it seamless to any software package. Intel claims that Alder Lake will be Intel’s best (ever? 2021?) performance-per-watt processor.

If leaks are to be believed, then Alder Lake looks set to offer an 8+8 design, although that has not been confirmed. Intel did not go into detail if Alder Lake will involve any next generation packaging, such as Foveros (which Lakefield does) – but in the Q2 2020 financial disclosures, it was said to be positioned for mobile and desktops. We expect Intel to discuss Golden Cove and Gracemont at some point next year, and then Alder Lake as an extension to those – we have already seen Intel documents regarding new instructions for each of these cores. My prediction is to come back this time next year, where we should have more to talk about.

Related Reading

- Intel Updates ISA Manual: New Instructions for Alder Lake, also BF16 for Sapphire Rapids

- Intel Roadmap Update: Alder Lake In H2’21, Ice Lake-SP Late This Year

- Intel’s 11th Gen Core Tiger Lake SoC Detailed: SuperFin, Willow Cove and Xe-LP

- The Intel Xe-LP GPU Architecture Deep Dive: Building Up The Next Generation

- The Intel Lakefield Deep Dive: Everything To Know About the First x86 Hybrid CPU

89 Comments

View All Comments

Spunjji - Monday, August 17, 2020 - link

Wasn't that the goal of HSA? I haven't heard about that in so long I've gone and presumed the concept is dead now.Meteor2 - Tuesday, August 18, 2020 - link

Too hard to programMark242 - Friday, August 14, 2020 - link

Oh No.I can already see the marketing from Intel and laptop vendors going like

"mega-ultra-high-performance TWELVE CORE CPU ..." (4 big+8 little)

When in reality it is slower than an AMD (or Intel) 8 core CPU. And I can see people falling for that kind of marketing as well ...

lmcd - Friday, August 14, 2020 - link

That was called Bulldozer.brucethemoose - Friday, August 14, 2020 - link

There was a lawsuit over that marketing scheme IIRC.lmcd - Friday, August 14, 2020 - link

Yes. I'm just saying I don't see the problem with this considering that each core has a separate fetch/decode/int/fp etc pipeline.Spunjji - Monday, August 17, 2020 - link

The problem's pretty similar (counting total cores without specifying resources per core), if indeed you believe that's is a problem in the first place. You do, so you'd have to do better on rationalising why one's okay and one's not.Spunjji - Monday, August 17, 2020 - link

That lawsuit was an absolute nonsense. In a technical sense it was without merit, and from a performance point of view you had to be a really specific kind of ignoramus to think you needed 8 cores but somehow failed to notice the reviews pointing out that the per-core performance was not up to Intel's standards.lmcd - Friday, August 14, 2020 - link

Honestly most highly-threaded workloads on a laptop don't need every thread to be crazy powerful anyway. A modern Atom core is actually up to snuff for most workloads as long as it isn't allocated the bottleneck thread. If you think about boost clocks and such, an Atom core would allow for nearby cores to have higher boost clocks. For the die space, each one would disproportionately benefit threaded workloads.Unlike Bulldozer, assigning to nearby cores shouldn't be a problem, so scheduling around these mixed cores should be relatively easy.

Spunjji - Monday, August 17, 2020 - link

Your comments here are amusing. Scheduling for Lakefield is already known to be *more difficult* than scheduling for Bulldozer was, because the cores don't have equal execution resources.If it were so easy they'd let you use the big and little cores at the same time; but they don't.