The Intel Lakefield Deep Dive: Everything To Know About the First x86 Hybrid CPU

by Dr. Ian Cutress on July 2, 2020 9:00 AM ESTPerformance Numbers: How To Interpret Them

On the previous page, we covered all three of the initial Lakefield designs. All three are very premium products, either offering a super light and thin clamshell with the Samsung, a foldable display with the Lenovo, or dual 9-inch displays in the case of the Microsoft device. Typically we see these sorts of devices paired with the best-in-class performance hardware, which can cost a lot depending on where it is coming from. Add in the device material cost, and we can easily go north of $999, $1499, or even higher when paired with lots of storage, or items like variable refresh displays. Make no mistake, Lakefield will end up in premium high-cost products.

This means that there will be a certain expectation of performance. Users won’t be satisfied if they get an expensive product with mid-range performance – if they’ve paid top dollar, they want it to exceed in all areas. Performance, battery life, and aesthetics all matter to the end-user when we’re dealing with things like flexible displays or new and exciting form factors on top of everything else.

Now don’t get us wrong here, Lakefield certainly fits many of the criterion of a premium product. It was specifically designed to fit into a small footprint by using novel and complex technology. By using the die-to-die bonding techniques and PoP memory, Intel has put in 174 mm2 of silicon into 12mmx12mm dimensions at only 1mm z-height. It leverages both Intel’s leading edge 10+ manufacturing node as well as Intel’s 22FFL high efficiency manufacturing node, and then optimized layout and manufacturing to ensure it has the most appropriate thermal characteristics for the design. There’s also the ultra-low idle power, supposedly measuring 2-3 mW, which has been an important characteristic in laptops that have been using smartphone processors. Offering substantial idle battery life is a key to marketing this type of product.

However, this page is about performance. Ultimately Lakefield can be compared to a number of products on the market. Numbers in brackets indicate big cores and small cores:

- Intel 7 W Lakefield (1+4) vs Qualcomm Snapdragon 7c (0+8)

- Intel 7 W Lakefield (1+4) vs Intel 6 W Goldmont+ Atom (0+4) N5030

- Intel 7 W Lakefield (1+4) vs Intel 5 W Amber Lake-Y (2+0) m3-8100Y

- Intel 7 W Lakefield (1+4) vs Intel 9 W Ice Lake-Y (2+0) 1005G1

| Comparison Table for Lakefield | |||||

| Intel i7-L16G7 |

AnandTech | Intel i3-1005G1 |

Intel m3-8100Y |

Intel N5030 |

Qualcomm SD 7c |

| Lakefield | SoC | Ice Lake-Y |

Amber Lake-Y |

Goldmont+ | Kryo |

| 1+4 | Core Config | 2+0 | 2+0 | 0+4 | 0+8 |

| 7 W | TDP | 9 W | 5 W | 6 W | ~7 W |

| 1 x SNC 4 x TNT |

CPU | 2 x SNC | 2 x SKL | 4 x GMN+ | 8 x Kryo |

| Gen 11 64 EUs 0.5 GHz |

GPU | Gen 11 32 EUs 0.9 GHz |

Gen 9 24 EUs 0.9 GHz |

Gen 9 18 EUs 750 MHz |

Adreno 618 |

| 4267 | LPDDR | 3733 | LPD3-1866 | 2400 | 4267 |

| Wi-Fi 6* | Wi-Fi | Wi-Fi 5* | - | - | Wi-Fi 6 |

| - | Modem | - | - | - | Cat15/13 |

One processor I missed out here is the Qualcomm Snapdragon 8cx, which is a 4+4 configuration that Qualcomm has specifically built for these sorts of mobile devices. The 4+4 configuration, on paper, might seem unfair to the 1+4 of Lakefield, whereas the 0+8 configuratrion of the Snapdragon 7c is more in line with what we might expect. However, the Snapdragon 7c isn’t actually inside any retail devices right now, having only been on display at Qualcomm’s own event in December.

The thing is, the Snapdragon 7c is set to be in devices competing at the $500 level against entry-level Intel Celeron devices. The 8cx is the premium chip, that ends up in the premium devices. This is where Intel will have difficulty.

On Intel’s own slides, the company performs two main comparisons.

- Benchmarks against Amber Lake-Y, the i7-8500Y in 5W mode

- Benchmarks where the i5-L16G7 runs in 1+4 and 0+4 modes

Benchmarks vs. Intel Amber Lake i7-8500Y

For the first point, Intel promotes the following against Amber Lake:

- +12% single threaded performance, measured by SPEC2006 (3.0 GHz vs 4.2 GHz)

- +70% graphics performance, 3DMark11 comparing HD615 (24 EUs, Gen 9.5 at 1.05 GHz, 2x4 GB LPDDR3-1866) vs HD (64 EUs, Gen11 at 500 MHz, 2x4 GB LPDDR4X-4267)

- +24% power efficiency, score per Watt on WebXPRT 3

- +100% AI workloads on graphics, ResNet50 batch 128 on OpenVINO, comparing

For each of these workloads, there’s something very obvious to pick at.

The first one is SPEC2006, not SPEC2017, and it’s comparing an Amber Lake core to a Sunny Cove core, which as we discussed should have +18% IPC. The frequency difference (assuming both were allowed to turbo to max) is 40% in the favor of Amber Lake, however the Lakefield has a 40% TDP advantage.

On the graphics performance, it’s a substantial mashup – Gen 9 vs Gen 11, 24 EUs vs 64 EUs, 1.05 GHz vs 500 MHz, LPDDR3-1866 vs LPDDR4X-4267. We know that Intel is going wide and slow with Lakefield, and the fact that Lakefield has an additional 40% TDP to help the graphics and CPU cores, I suspect that each chip was battling to find the right balance of power to the CPU or power to the GPU.

On the AI workload, this benchmark has been hand-picked. Intel has done an offline Resnet-50, and run the CPUs in batches. With the GPU being wide and slow, there is the question as to whether the GPU would be competitive in batch-1 type scenarios. Again, there’s also a TDP difference here, as well as a memory difference that explains the raw performance change.

Benchmarks Against Lakefield in 1+4 Mode against 0+4 Mode

For the second set of benchmarks, Intel promotes +33% higher web performance and 17% better power efficiency by adding a big core to a quartet of small cores – essentially comparing a full fat Lakefield against a quad-core Atom design.

What this means is that Lakefield, by and large, will perform the same as a quad-core Atom in almost all tasks, especially heavy tasks. Given that we haven’t had a new Atom platform since 2017, and it’s been even longer since we saw Atom notebooks in a big way, I can guarantee that a lot of users will look at Lakefield and compare it to big-core designs. Intel has also tripped over its own feet in not comparing the performance to any of Qualcomm’s designs. The cost would seem to put it square against the Snapdragon 8cx, however the core layout suggests the 7c would be a fairer fight. Putting Intel’s AI test against Qualcomm’s hardware would also make for an interesting comparison.

Another thing to note, which Intel glossed over, that most people are going to be really concerned about.

What The Big Core Is Actually For

I’ve mentioned a few times in this piece that the big Sunny Cove core is more for end-user latency driven interactions, such as tapping on the screen, typing on the keyboard. When it comes to loading a web page, this blurs the line between response and workload, depending on the browser and how it manages threads.

Now, if we take a traditional high load single threaded workload, such as say, rendering. Which core will it run on? A lot of Intel’s marketing materials, as well as considering the layout of the chip, might get a reasonable end-user to expect that it would run on the high-performance single core. However, consider two things: firstly, rendering a frame is not a latency-driven interaction. Secondly, how many processes are running in the background? Both of these elements would point to the operating system pushing the workload, despite being single threaded, onto the Tremont Atom cores.

At the time of writing, Notebookcheck is the only outlet to publish data from an early look on Samsung’s Galaxy Book S. If we take a single threaded rendering workload, like Cinebench R15, then Lakefield scores 88 points, while the Amber Lake that Intel used in its slides scores 129, a +46% performance uplift to the older Amber Lake system. What in the world is going on? It’s running on the Atom cores.

Our recommendation, for anyone wanting to test the performance of that single Sunny Cove core, is to implement an affinity mask on the software being used. If the software only knows that one core exists, then it can only run on that core. This is how we suspect that Intel achieved the single core performance gains in benchmarks like SPEC2006. However Intel has more tools at its disposal – there’s a chance that the scheduler for these systems might ignore affinity masks in order to maintain a thermal balance in the design. We must wait until we get a sample in for ourselves.

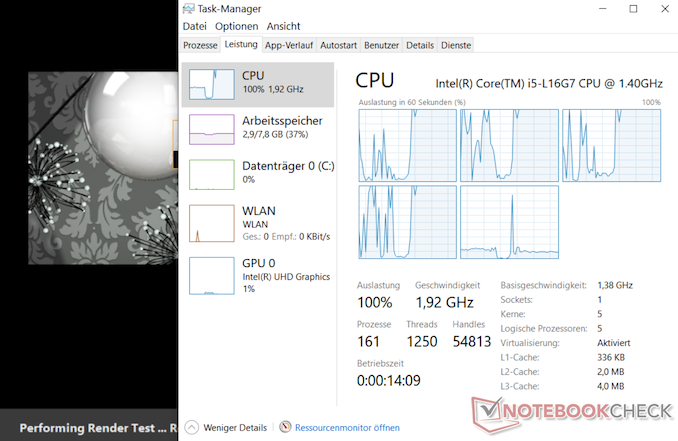

To a certain extent we see this in the Cinebench R15 multi-threaded test. With a standard 5 thread processor, if you run a standard nT test, we expect it to fill all the cores to give the best performance. In Notebookcheck’s article, we can see that the scheduler has evicted the workload from the big core. This is likely due to power/thermal hotspot reasons.

Source: Notebookcheck

In the task manager on the right, we see the first four Atom cores running at 100% while in the multi-threaded test, while the large Sunny Cove core is relatively idle. Note that the CPU is running at 1.9 GHz, and not the 2.8 GHz that Intel has promoted is the all-core turbo for this product.

But the bottom line is that in most cases, expect Lakefield to perform similar to four Atom cores, just above Goldmont Plus, and not like any of the Skylake/Ice Lake Core products and its derivatives.

221 Comments

View All Comments

AhsanX - Thursday, July 2, 2020 - link

The Sunny Cove has AVX-512 but Tremont cores don,t have any AVX. So Intel disabled AVX on the Sunny Cove core too, as heat was gonna be a problem if they let it enabled.ikjadoon - Thursday, July 2, 2020 - link

Did we read the same article? AVX-512 was completely removed (i.e., physically) from the Sunny Cove dies because of Windows 10 compatibility problems.Windows was never built for x86 heterogeneous processing and still cannot do anything close now in 2020 (perhaps that would've been a smarter investment than going all-in on touch in 2008!).

Intel & Microsoft remain stuck in late 2010s for their low-power / mobile-first / thin-client transition caused by the dominating success of smartphones & ARM-based architectures wiping out anything of interest in low-power x86.

There's a reason Intel just nearly stopped all development on Atom: nobody give a crap about the Pentium Silver & Celeron CPUs.

ikjadoon - Thursday, July 2, 2020 - link

*gaveJorgp2 - Thursday, July 2, 2020 - link

>There's a reason Intel just nearly stopped all development on Atom: nobody give a crap about the Pentium Silver & Celeron CPUs.Lol, no

ProDigit - Friday, July 3, 2020 - link

The $160 laptop I purchased from hp, with an N5000 in it, works really well!Would have been better if used on a desktop, and the core count was quadrupled.

extide - Thursday, July 2, 2020 - link

It's not a windows issue. Even if you ran Linux or any other OS on here you would have to run with CPU's all supporting the same ISA. ARM specifically designs cores to pair up together such that they have the exact same ISA (instruction support) so this isn't an issue in cell phones.I mean theoretically you could have the processors support a slightly different ISA and have it throw an interrupt if it tried to execute an instruction that the current core didn't support but a different one did and then the scheduler would have to move that thread to the other core. That could get really janky though, which is why nobody has talked about doing this yet.

Also, they said in this article that even though Intel said they removed the AVX512 units -- it can still be seen in the die shots.

Also, Intel didn't stop development on Atom -- this chip has a brand new core and their public roadmaps have several more in the future.

reggjoo1 - Tuesday, July 7, 2020 - link

They’re gonna have to develop more for atom, and get into the right “governor “ for crossover operation, more than scheduler tweaks. They have a lot to learn, and it may come down to the quality over the I/O system for these to really succeed. As long as their "ego" doesn't get in their way, and they learn from the "smartphone arena, they might have something for X86.dotjaz - Friday, July 3, 2020 - link

Did we read the same article? AVX-512 was clearly not removed.dotjaz - Friday, July 3, 2020 - link

There, "Intel has stated on the record repeatedly that they removed it. The die shot of the compute silicon shows that not to be the case." If you can read.jeremyshaw - Friday, July 3, 2020 - link

That was a later edit. Originally Ian claimed it was removed.