GeForce GTX 970: Correcting The Specs & Exploring Memory Allocation

by Ryan Smith on January 26, 2015 1:00 PM ESTDiving Deeper: The Maxwell 2 Memory Crossbar & ROP Partitions

Now that we have a basic understanding of the proper specifications of the GTX 970 we can dig deeper into its architecture and layout. As we mentioned previously, the GTX 970 ships with an unusual configuration, one we’ve never quite seen before. In it, thanks to a new feature of the Maxwell architecture, NVIDIA has been able to disable part of a ROP/Memory Controller partition, something that they could not do on Kepler or earlier generation designs. As a result of this the intended behavior of the GTX 970 is different than the GTX 980 or any theoretical Maxwell part with a completely disabled ROP/MC partition.

The biggest impact of this configuration is that it creates the segmented memory conditions NVIDIA outlined in their earlier statement. Due to performance issues from the unbalanced ROP/MC partition, NVIDIA segments the memory into a high-performance 3.5GB segment – what they refer to as segment 0 – and a low-performance 512MB (0.5GB) segment containing the rest of the RAM. It is this segmentation that results in some of the previously-unusual memory allocation behaviors and memory bandwidth benchmarks on the GTX 970.

But in order to understand just why the segments exist, how they are allocated, and how they influence performance, we first need to learn about the Maxwell memory crossbar.

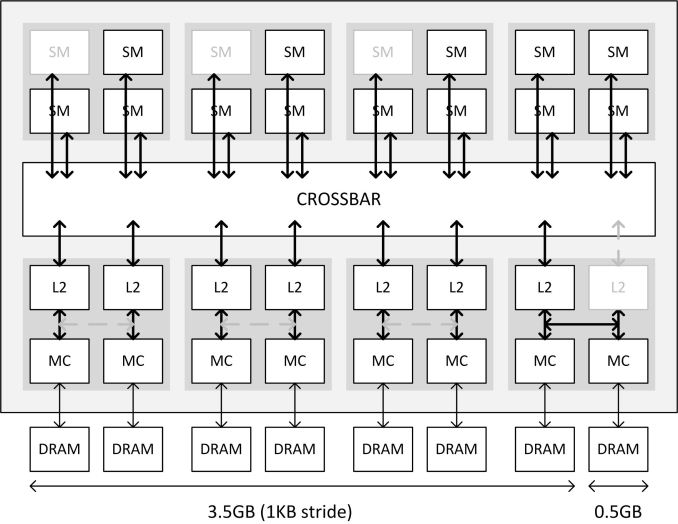

In the above diagram from NVIDIA, NVIDIA illustrates at a high-level overview how the Maxwell memory crossbar is laid out, and specifically how it’s configured for GTX 970. In it we have the 16 GM204 SMMs at the top connected to the crossbar, meanwhile below we have 4 ROP/MC partitions, with each partition divided up into individual ROP/L2 units and memory controllers. Note that the specific units disabled on any GTX 970 chip will vary – it’s not necessarily the 1/3/5 SMMs or the last ROP/MC partition – but from a high level overview this is consistent for GTX 970 regardless of which specific physical units have been disabled.

In any case, while the crossbar shows how the SMMs and ROP/MC partitions are connected via the crossbar, memory segmentation is really a story about the ROP/MC partitions. The SMMs do not play a role in how GTX 970’s memory is configured – the crossbar abstracts all of that – and the crossbar itself matters only in as much as the ROP/MC partitions are connected to it.

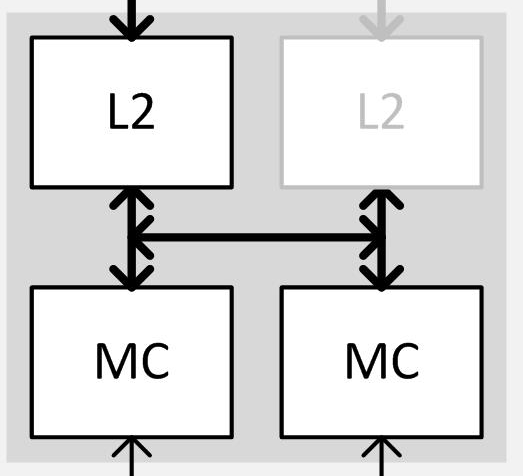

When it comes to the ROP/MC partitions then, we can see first-hand in the GTX 970 what’s new in the architecture. In Kepler and previous generation designs, NVIDIA’s granularity for disabling ROP/MC partitions was all or nothing – either the entire partition was turned on or the entire partition was turned off. However starting with Maxwell, NVIDIA has gained the ability to disable the individual ROP/L2 units within a partition, allowing one of the two ROP/L2 units to be disabled. This essentially introduces a 3rd possible option: a partially-enabled ROP/MC partition, backed by two memory controllers and a single ROP/L2 unit. Meanwhile the memory controllers are still tied together, and disabling one of them requires disabling the entire partition.

| NVIDIA ROP/Memory Controller Configuration Options | |||

| Kepler | Maxwell | ||

| ROP/MC Partition Fully Enabled | ROP/MC Partition Fully Enabled | ||

| N/A | ROP/MC Partition Partially Disabled | ||

| ROP/MC Partition Fully Disabled | ROP/MC Partition Fully Disabled | ||

It’s this option that the GTX 970 leverages, and in doing so becomes the first Maxwell part to use this feature. NVIDIA has disabled 1 ROP/L2 unit, removing 8 “ROPs” (or rather 1 unit capable of 8 pixels/clock) and 256KB of L2 cache from the GTX 970. This is why the GTX 970 is left with 56 ROPs spread over the 4 partitions, along with 1.75MB of L2 cache.

Meanwhile there’s one other new feature here that’s activated only on the partially disabled partition, and that’s the link between the first and second units of the ROP partition. Typically each ROP/L2 unit would have a link to a port on the crossbar and a link to its own dedicated 32-bit memory controller channel; however because GTX 970 disabled a ROP/L2 unit, the “buddy” link comes in to play. This link is essentially the lynchpin of Maxwell’s new partial disable functionality, and allows the second half of the memory controller to stay active. This link only needs to be active when a ROP/L2 unit is disabled, and NVIDIA has confirmed that it is a full bandwidth link identical to the normal ROP/L2 to MC link, meaning it’s capable of 4 32 byte requests per clock (2 reads and 2 writes). Ultimately this link is what makes a partially disabled partition possible, and is also what makes it possible to have the full 256-bit memory bus present and active in spite of the lack of a ROP/L2 unit and its associated crossbar port.

Finally, because of this configuration and the lack of a ROP/L2 unit we get to the memory segments. Although the full 256-bit memory bus is present and active on GTX 970 and capable of providing 224GB/sec of combined memory bandwidth between the DRAM modules and the memory controllers, it’s a bit of a misnomer to say the card has that much bandwidth between the memory controllers and everything else, at least in the same sense that the GTX 980 does.

Like virtually every other operation on a GPU, memory accesses are done in parallel to improve throughput. On a fully enabled card such as GTX 980 these operations are striped across all of the memory controllers in what NVIDIA calls a 1KB stride. In doing this, each and every 32 bit memory channel needs a direct link to the crossbar through its partner ROP/L2 unit. However in the case of the GTX 970 a wrench is thrown into the works, as there are 7 crossbar ports and 8 memory channels.

Ultimately due to the design of the crossbars and the memory controllers, it is not possible for 1 crossbar port to carry the full load of 2 memory channels in all circumstances. The crossbar port and its attached ROP/L2 unit can access both memory channels at once, splitting up the 4 operations among them, but there is only 1 read return bus and 1 write data bas, and hence in practice it cannot issue identical operations to both memory channels at once . As a result NVIDIA has segmented the GTX 970’s memory into the now-familiar 3.5GB and 512MB segments. In the case of the 3.5GB segment, this behaves otherwise identically to a fully enabled card such as the GTX 980, with the 1KB stride being striped over 7 crossbar ports, and hence 7 DRAM modules. Meanwhile the 8th and final DRAM module sits in its own 512MB segment, and must be addressed by the crossbar on its own.

This in turn is why the 224GB/sec memory bandwidth number for the GTX 970 is technically correct and yet still not entirely useful as we move past the memory controllers, as it is not possible to actually get that much bandwidth at once when doing a pure read or a pure write. In the case of pure reads for example, GTX 970 can read the 3.5GB segment at 196GB/sec (7GHz * 7 ports * 32-bits), or it can read the 512MB segment at 28GB/sec, but it cannot read from both at once; it is a true XOR situation. The same is also true for writes, as only one segment can be written to at a time.

Unfortunately what this means is that accessing the weaker 512MB segment blocks access to the stronger 3.5GB segment if both memory operations are identical; or put another way, using the 512MB segment can harm the performance of the 3.5GB segment. For example, if we want to issue reads to both segments at once, reading the 512MB segment blocks any other reads to the 3.5GB segment for that cycle. If the 3.5GB segment is blocked in this fashion and doesn't have a non-blocking write to work on instead, it would have to go idle for that cycle, which would reduce the effective memory bandwidth of the 3.5GB segment. This means that taken over time in our example, the larger the percentage of the time the crossbar is reading the 512MB segment, the lower the effective read memory bandwidth would be from the 3.5GB segment.

Despite all of this, achieving peak memory bandwidth performance on the GTX 970 is still possible, but it requires much more effort since simple striping will not do the trick. The easiest and most effective solution in this regard is to interleave reads and writes over the segments, such that one segment is writing while another segment is reading. Interleaving in this fashion allows both segments to work at once – avoiding the blocking effect of the shared read and write buses – and makes it more likely that both segments are doing useful work rather than waiting for their turn on an operation. However because this is only applicable to situations where more than 3.5GB of VRAM is in use and both segments are necessary, this means it's only theoretically possible to achieve 224GB/sec when more than 3.5GB of VRAM is in use. In any situations below 3.5GB we are de-facto limited to just the larger segment, in which case there are only 7 memory channels (196GB/sec) to stripe memory operations across. NVIDIA could of course interleave operations sooner than that and use both segments more often, but due to the blocking effect we've discussed before the performance hit from using the 512MB segment can quickly become greater than any gains.

The end result of all of this is that the GTX 970 has a unique memory layout that needs to be accounted for by the operating system and NVIDIA’s drivers, as the use of multiple segments adds a new level of complexity to optimizing memory performance. Unequal in size and performance, among the two segments the 3.5GB segment is a larger, faster, and otherwise more preferable segment to the 512MB segment. Which means from a logical hierarchical perspective, the 512MB segment essentially serves as an additional layer of memory between the main VRAM and system memory, being slower than the 3.5GB segment but offering almost 2x the performance of going out over the PCIe bus to system memory.

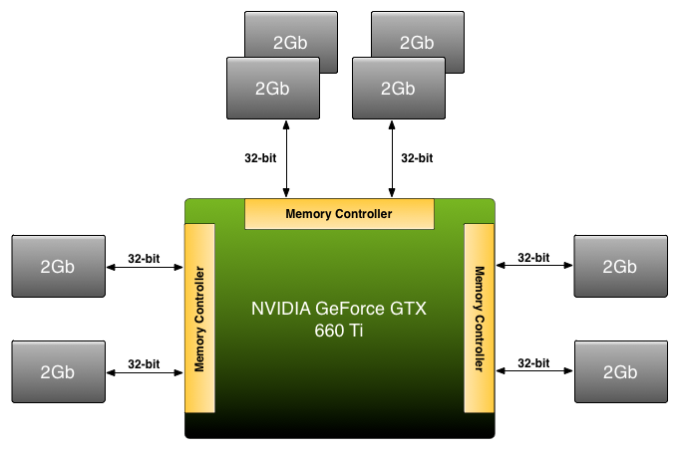

The upshot here is that while this is the first time NVIDIA has used this specific ROP/MC configuration in a product, this is not the first product they have designed with segmented or otherwise unbalanced memory configurations. Since the GTX 500 series, on some midrange SKUs NVIDIA has used unbalanced/asymmetrical memory configurations, most recently on the GTX 660 and GTX 660 Ti. In the case of both of those cards, NVIDIA utilized a 192-bit memory bus with 2GB of VRAM attached, which meant that some memory controllers had more VRAM attached to them than others. The end result as it turns out is very similar, and while NVIDIA has never explained in-depth how they handle memory allocation on those cards, it turns out that it’s very similar to GTX 970’s memory segmentation. Which is to say that NVIDIA actually has multiple generations of experience with segmented memory, and this is not the first time they have implemented it. Rather this is first time we’ve seen such a configuration on a high-performance card such as the GTX 970.

For Comparison: GTX 660 Ti's Unbalanced Memory Bus

| NVIDIA Maxwell Family Memory Controller Configurations | |||

| Part | Memory Segments | ||

| GTX 980 | 1 Segment (4x8 MC) | ||

| GTX 970 | 2 Segments (4x7 MC) | ||

| GTX 980M | 1 Segment (4x8 MC) | ||

| GTX 970M | 1 Segment (3x6 MC) | ||

| GTX 965M | 1 Segment (2x4 MC) | ||

As for why NVIDIA is using such a configuration here, the crux of the matter is money and yields. Without the ability to partially disable a ROP/MC partition, NVIDIA would either have to spec a card to use a fully enabled partition – essentially reducing yields for that card and driving up costs – or disable the entire partition and lose all of the benefits of the additional ROPs, memory, and the memory controller. This finer granularity allows NVIDIA to better control how they harvest bad chips and what resulting configurations they bring to market, along with making a single ROP/L2 defect less harmful to overall performance by keeping the rest of a partition online. Otherwise, to stick with a “balanced” configuration with as many crossbar ports as DRAM modules would result in either a higher spec GTX 970, or a lower spec card with a 192-bit memory bus.

In the grand scheme of things then, depending on how you want to define memory capacity the GTX 970 can be said to have either 3.5GB of VRAM or 4GB of VRAM. Only the first 3.5GB segment is a high-speed (full bandwidth) segment, and for naïve operations this is the segment that software will want to use. However the final 512MB segment is accessible, and despite its lower performance it is still usable and still far better than going to system memory, in which case GTX 970 has and can access a full 4GB of VRAM. This means that both answers can be correct, and like so many other facets of modern technology, the true answer is often more complex than a single number.

398 Comments

View All Comments

slickr - Monday, January 26, 2015 - link

O come on. You sound like Nvidia PR. So after working months/years on this architecture, you won't take several days rest and look at some of the reviews on your baby, on your product? No one in their company did? No one even skimmed through the first page of reviews and news?We've had reviews from when the cards officially launched, to months later reviews of custom cards, etc...

To me you sound like you are on Nvidia's pay check. I'm sorry, but I expect critical view from the media, not PR talk. Either you change the definition of this site from "Website" to "fansite" or start doing critical journalism, not this white washing PR bullshit!

Ryan Smith - Monday, January 26, 2015 - link

To truly understand this, you probably would need to have been on the phone with Jonah. The team that designed the architecture is not the team that picked the individual product configurations, and as a result they have no clue how many ROPs a part is supposed to have. Never mind the fact that they haven't looked at the architecture in a year or more.Modern product development is highly specialized, with each team working on its own little niche. This means they're generally blind to what everyone else is doing.

Whether you find that answer satisfactory or not is up to you. But the employees reading the review are generally not going to be the employees who know that 64 is the wrong number of ROPs on one specific SKU.

OrphanageExplosion - Monday, January 26, 2015 - link

I find that hard to believe to be honest, Ryan.You think a guy like, say, Tom Petersen who knows the product and knows the press inside out doesn't read the reviews and doesn't know the true specification of the GTX 970?

anandreader106 - Monday, January 26, 2015 - link

"....But the employees reading the review are generally not going to be the employees who know that 64 is the wrong number of ROPs on one specific SKU."So the employees that would know that 64 was the wrong number do not read reviews on the internet?

JarredWalton - Monday, January 26, 2015 - link

Correct, because they're doing hardware design. I highly doubt Jonah even does more than a cursory glance at most of the reviews. He's paid too much to be doing that. Even guys like Jen Hsun aren't going to read all the hardware reviews -- they'll get the executive summary of how the launch went.mapesdhs - Monday, January 26, 2015 - link

In the 1990s I knew someone involved with CPU development who told me about the nature

of his work, the pay, the hours, etc. I full agree with Jarred, these people work very hard and

are extremely well paid; they're not going to be reading reviews, they're far too busy, almost

certainly working on whatever's coming next.

Ian.

alacard - Monday, January 26, 2015 - link

Hook, line, and sinker. Watching all these tech journalists rushing to Nvidia's defense is just priceless. Guys, when your master's knock some shit off their table for you to eat, have some self respect and try to recognize it for what it is so you can treat it accordingly in your write-ups because as it stands right now you're all Exhibit A in the inevitable inquiry into the death and total collapse of the fourth estate.dragonsqrrl - Monday, January 26, 2015 - link

Yes, all these credible tech journalists are conspiring with Nvidia to cover this all up. Has Demerjian issued a statement yet?yannigr2 - Tuesday, January 27, 2015 - link

When AMD released Hawaii and the hardware sites where seeing the core clock throttling, it was not about performance, but about the core clock of the GPU. Now that Nvidia lied about the specs, it's not about the specs, but about how small is the performance penalty. Do you see the difference?OrphanageExplosion - Tuesday, January 27, 2015 - link

So nobody from the NVIDIA tech team read the reviewer's guide either then? I genuinely think it probably was a mistake, but the notion that nobody at NVIDIA noticed that *all* the public specs on the card are incorrect beggars belief and the notion of journalists *literally* making excuses for NVIDIA is stunning.The bottom line is this: GTX 970 is a fantastic card, the perf is stunning, but NVIDIA released dodgy specs, didn't correct them when they became public and should have been transparent about the 512MB partition right from the get-go. It wouldn't have changed anything in the reviews, and the card would still have been a huge success, 56 ROPs or not.

This is far less a perf issue and much more about trust.