It Begins: AMD Announces Its First ARM Based Server SoC, 64-bit/8-core Opteron A1100

by Anand Lal Shimpi on January 28, 2014 6:35 PM EST- Posted in

- CPUs

- IT Computing

- AMD

- Arm

- Opteron

- Enterprise

- Enterprise CPUs

- Opteron A1100

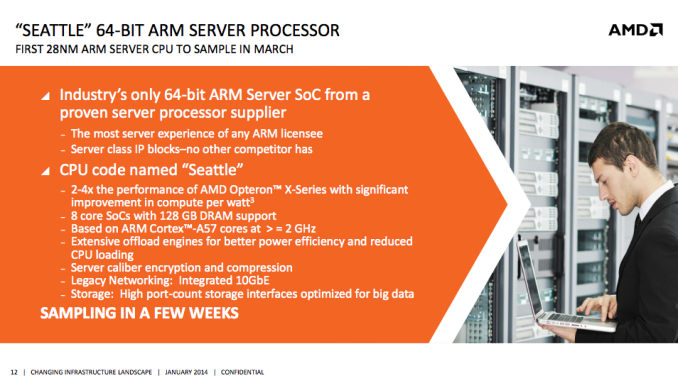

Around 15 months ago, AMD announced that it would be building 64-bit ARM based SoCs for servers in 2014. Less than a month into 2014, AMD made good on its promise and officially announced the Opteron A1100: a 64-bit ARM Cortex A57 based SoC.

The Opteron A1100 features either 4 or 8 AMD Cortex A57 cores. There's only a single die mask so we're talking about harvested die to make up the quad-core configuration. My guess is over time we'll see that go away entirely, but since we're at very early stages of talking about the A1100 there's likely some hedging of bets going on. Each core will run at a frequency somewhere north of 2GHz. The SoC is built on a 28nm process at Global Foundries.

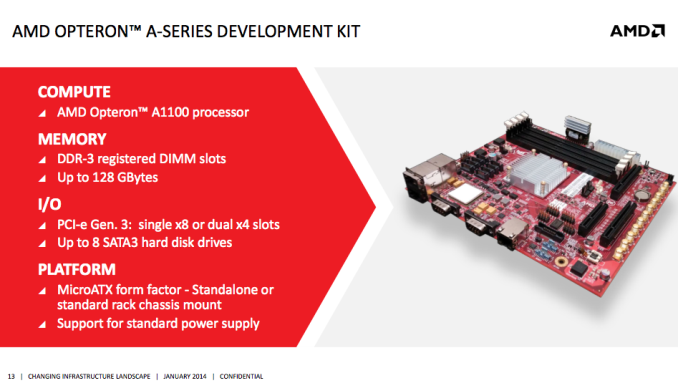

Each pair of cores shares a 1MB L2 cache, for a total of up to 4MB of L2 cache for the chip. All cores share a unified L3 cache of up to 8MB in size. AMD designed a new memory controller for the Opteron A1100 that's capable of supporting both DDR3 or DDR4. The memory interface is 128-bits wide and supports up to 4 SODIMMs, UDIMMs or RDIMMs. AMD will be shipping a reference platform capable of supporting up to 128GB of Registered DDR3 DIMMs off of a single SoC.

Also on-die is an 8-lane PCIe 3.0 controller (1 x8 or 2 x4 slot configurations supported) and an 8-port 6Gbps SATA controller. AMD assured me that the on-chip fabric is capable of sustaining full bandwidth to all 8 SATA ports. The SoC features support for 2 x 10GbE ports and ARM's TrustZone technology.

AMD will be making a reference board available to interested parties starting in March, with server and OEM announcements to come in Q4 of this year.

It's still too early to talk about performance or TDPs, but AMD did indicate better overall performance than its Opteron X2150 (4-core 1.9GHz Jaguar) at a comparable TDP:

| AMD Opteron A1100 vs. X2150 | |||||||||

| CPU Core Configuration | CPU Frequency | SPECint_rate Estimate | SPECint per Core | Estimated TDP | |||||

| AMD Opteron A1100 | 8 x ARM Cortex A57 | >= 2GHz | 80 | 10 | 25W | ||||

| AMD Opteron X2150 | 4 x AMD Jaguar | 1.9GHz | 28.1 | 7 | 22W | ||||

AMD alluded to substantial cost savings over competing Intel solutions with support for similar memory capacities. AMD tells me we should expect a total "solution" price somewhere around 1/10th that of a competing high-end Xeon box, but it isn't offering specifics beyond that just yet. Given the Opteron X2150 performance/TDP comparison, I'm guessing we're looking at a similar ~$100 price point for the SoC. There's also no word on whether or not the SoC will leverage any of AMD's graphics IP.

The Opteron A1100 is aimed squarely at those applications that either need a lot of low power compute or tons of memory/storage. AMD sees huge demand in the memcached space, cold storage servers and Apache web front ends. The offer is pretty simple: take cost savings on the CPU front and pour it into more DRAM.

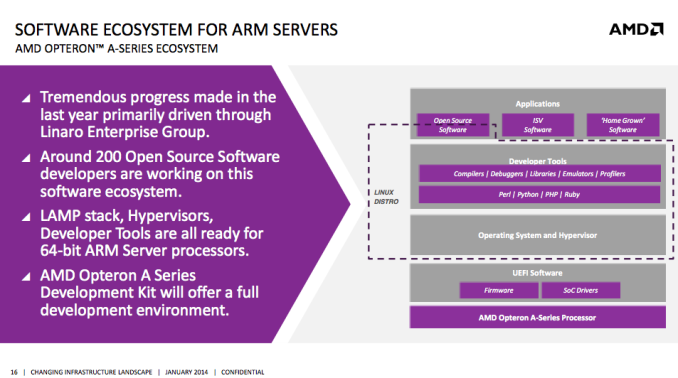

Early attempts at ARM based server designs were problematic given the lack of a 64-bit ARM ISA. With ARMv8 and the Cortex A53/A57 CPUs, that's all changed. I don't suspect solutions like the Opteron A1100 to be a knockout success immediately, but this is definitely the beginning of something very new. Of all of the players in the ARM enterprise space, AMD looks like one of the most credible threats. It's also a great way for AMD to rebuild its enterprise marketshare with a targeted strike in new/growing segments.

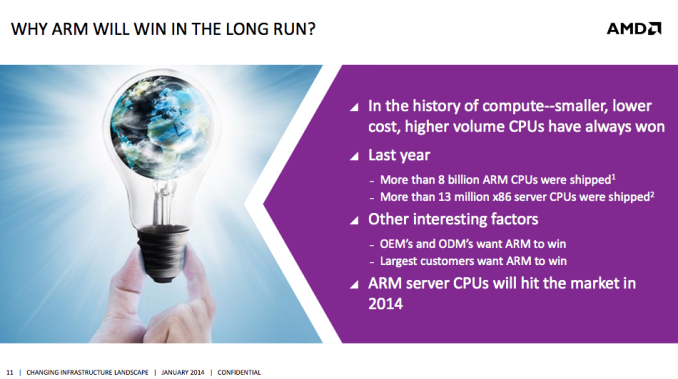

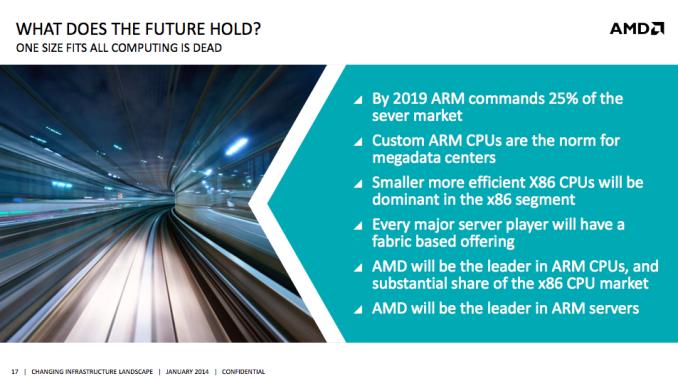

AMD's Andrew Feldman included one of his trademark reality check slides in his Opteron A1100 presentation today:

Lower cost, high volume CPUs have always won. That's how Intel took the server market to begin with. The implication here is that ARM will do the same to Intel. Predicting 25% of the server market by 2019 may be feasible, but I'm not fond of making predictions for what the world will look like 5 years from now.

The real question is what architecture(s) AMD plans to use to get to a leadership position among ARM CPUs and a substantial share of the x86 CPU market. We get the first hint with the third bullet above: "smaller more efficient x86 CPUs will be dominant in the x86 segment".

122 Comments

View All Comments

dealcorn - Tuesday, January 28, 2014 - link

The comparison to high-end Xeon sounds fanciful. Low-end Xeon (Avoton/Rangerly) is already at 20/21 watts which is substantially lower that Seattle's 25 watts. The target market is sensitive to efficiency. Unless AMD can identify specific niches where Seattle efficiency reigns, this sound like a pipe dream.HisDivineOrder - Tuesday, January 28, 2014 - link

It's interesting to read how AMD thinks ARM is going to win out over x86. Thing is, I think the real argument AMD must make is how AMD themselves are going to win out against other companies also going ARM in much the same way.In x86, there's Intel and then there's AMD (and stories tell of a mythical VIA as well), but when you go ARM, you're one of bajillions. AMD doesn't stand out.

siliconwars - Tuesday, January 28, 2014 - link

Yeah I guess AMD doesn't stand out if you don't actually read the article.davegraham - Tuesday, January 28, 2014 - link

relatively ignorant, HisDivineOrder. AMD will be one of SEVERAL in the ARM server space. remember, Calexda has actually needed to restructure and others in the space (think: nVidia) are relatively unproven when it comes to server technology. AMD has the ability to be rather agile here and can target devices toward highly scaled and integrated systems like: Moonshot, SeaMicro, etc. this is a first shot in the battle for scaled/dense systems that will most predominantly rely on more SoC style systems than core x86 manus can provide.pugster - Wednesday, January 29, 2014 - link

These cpu's are designed to replace the servers that are currently used by datacenter farms of the likes of google, yahoo, amazon and facebook.name99 - Wednesday, January 29, 2014 - link

This is the difference between amateurs and professionals. Amateurs think it is all about the specs of the core, professionals know that (for the space of interest) it is all about memory and IO.Yes AMD are shipping a standard ARM core, like everyone else in this space. BUT they claim they have superior skills in memory controllers and IO and, so far at least, there is no reason to doubt them.

KenLuskin - Wednesday, January 29, 2014 - link

Its NOT simply ARM, its ALL the IP sever blocks that AMD owns!Its the FABRIC for DENSE servers!

Too bad you are CLUELESS

jimjamjamie - Thursday, January 30, 2014 - link

There is no need to be upsetmczak - Tuesday, January 28, 2014 - link

Sure about that L2 config?My guess would have been 2MB per 4 cores, not 1MB per 2 cores. Because this is what a basic cluster containing a57 cores straight from arm without any modifications does.

RogerShepherd - Wednesday, January 29, 2014 - link

Straight from the ARM website. A57 can be 1-4X SMP within a single processor cluster (i.e. 1-4 cores with a shared L2 cache). Multiple coherent SMP processor clusters through AMBA® 5 CHI or AMBA® 4 ACE technology.So, it is perfectly possible that AMD has chosen 4 clusters of 2-cores+L2.