More Details on the Intel Atom Emerge

by Anand Lal Shimpi on March 6, 2008 8:00 PM EST- Posted in

- CPUs

The Moorestown Update: Atom in Smartphones

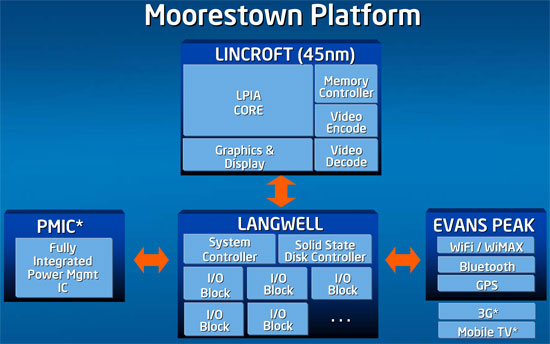

The successor to Menlow is Moorestown. Also built on a 45nm process, Moorestown is a highly integrated version of Menlow composed of the following components:

1) Lincroft System on a Chip (SoC)

2) Langwell South Hub

3) PMIC

4) Evans Peak Networking

Moorestown is composed of two chips: a north hub and a south hub. The Lincroft SoC is the north hub and it features a LPIA (Low Power Intel Architecture) CPU core (Silverthorne derivative), on-die graphics and on-die memory controller. Both video encode and decode hardware are also included on-die. This is a big step from Menlow because the GPU is now built on a 45nm process since it’s contained on the CPU die itself. The on-die memory controller should also help performance of the in-order core which is highly dependent on receiving dependent data as quickly as possible.

The Langwell south hub is an extremely focused piece of silicon given how highly integrated the Lincroft north hub/CPU is. Langwell is composed of a system controller, solid state disk controller and I/O blocks for things like USB or audio.

The Power Management IC (PMIC) plays a mystery role at this point. Intel is just revealing that it handles power management for the platform yet not fully detailing its active roles. The PMIC interfaces with the Langwell south hub which is being licensed to 3rd parties to actually make the PMIC.

The final component of Moorestown is the Evans Peak networking hub, which is made up of Intel and non-Intel silicon. Intel will enable Wi-Fi, WiMAX, Bluetooth and GPS while 3rd party vendors can supply chips to enable things like 3G on Moorestown platforms.

As we mentioned before, Moorestown rids the platform of any PCI bus which apparently precludes it from being used with Windows Vista, because of this all Moorestown based MIDs will be running Linux. Linux is a far better fit for something like Menlow or Moorestown simply because the performance levels are too low to be used with a hog like Vista. Vista can work on these platforms, just not with iPhone-smoothness.

Thanks to the integration made possible with Moorestown idle power will be reduced by a factor of 10x over Menlow. With such a low idle power, voice applications now become possible with Moorestown.

Moorestown will allow Intel’s Atom CPU to exist in larger smart phones (4 - 5” size), while its successor in 2010/2011 will use the magic of Intel’s 32nm process to finally get into something iPhone-sized.

12 Comments

View All Comments

psychobriggsy - Friday, March 7, 2008 - link

Through use of Moore’s law allowing for better integration of silicon and smaller, less power hungry transistors, Intel hopes to be at power-parity with ARM (both idle and active) within the next 3 or so years - all while being significantly faster, at least for the next 5.Yeah, yeah, and ARM doesn't benefit from Moore's Law?

Intel hopes to be where ARM SoCs (far more integrated that Mooretown) have been for several years ... in another three. Maybe. Intel will have the process on their side. That's about it.

In the meantime, given the excellent performance of the iPhone on a 90nm 412MHz ARM11 core (with 1GHz+ available, and multi-core as well with Cortex) I don't see any imminent desire for Apple to switch to these offerings for the iPhone and iPod Touch. I think the release of their SDK suggests this as well - sure, they could make everyone port their software in a mere three years ... or not.

I just don't think that even Moorestown++ will be anywhere near what Apple need - not integrated enough, not frugal enough. They're not going to make an iBrick (in comparison).

nubie - Friday, March 7, 2008 - link

Are ARM SOC's just now moving to 65nm? Intel can push because it has the fab capability and IP and talent and resources.The iPhone being x86 means no more seperate Dev on two processor platforms, the iPhone will use the same progs as the desktop OS, no porting will be done, it will open up the handheld to all the companies already making OSX software, a "port" of any desktop app reasonably suited will be very very easy.

I wonder if Intel will allow a separate memory bus for the RAM, if so this would make it truly competitive, even a second DDR3 populated with SoDimm low latency high speed would do wonders for it. I am thinking of the HTPC and desktop markets of course (and the non-existent high performance hand held gaming market)

bebesito21 - Friday, March 7, 2008 - link

Yeah, so by 2015 Intel plans on having this ready? Aren't they a little behind? Seems like IBM already has this plan rolling. The Cell processor already has multiple "children" cpus waiting for a controller CPU to tell them what to do. This is, in my opinion, the best way to design chips because no developer wants to waste time writing programs that take advantage of multiple thread capable CPUS - they rather the hardware figure it out. Its hard enough to use 2 out of 4 cores on a quad core now..imagine 32 cores!I wish they would give us a socket on the motherboards for a GPU chip. Then they can do multi-core cpus and multi-core dedicated gpus with new ultra fast buses to link. Plus I don't want Intel completly taking over all chip making...that would at the least cut out NVDIA who doesn't make CPUs. They backed the PS3 though so they might help push the Cell.

LSnK - Friday, March 7, 2008 - link

The PPE doesn't auto-magically tell the SPEs what to do. It's vastly more difficult to program for the Cell than a standard multicore CPU. It isn't going to save developers any time.Thatguy97 - Tuesday, May 26, 2015 - link

Intel was right lolbebesito21 - Friday, March 7, 2008 - link

Yeah, so by 2015 Intel plans on having this ready? Aren't they a little behind? Seems like IBM already has this plan rolling. The Cell processor already has multiple "children" cpus waiting for a controller CPU to tell them what to do. This is, in my opinion, the best way to design chips because no developer wants to waste time writing programs that take advantage of multiple thread capable CPUS - they rather the hardware figure it out. Its hard enough to use 2 out of 4 cores on a quad core now..imagine 32 cores!I wish they would give us a socket on the motherboards for a GPU chip. Then they can do multi-core cpus and multi-core dedicated gpus with new ultra fast buses to link. Plus I don't want Intel completly taking over all chip making...that would at the least cut out NVDIA who doesn't make CPUs. They backed the PS3 though so they might help push the Cell.

bebesito21 - Friday, March 7, 2008 - link

Yeah, so by 2015 Intel plans on having this ready? Aren't they a little behind? Seems like IBM already has this plan rolling. The Cell processor already has multiple "children" cpus waiting for a controller CPU to tell them what to do. This is, in my opinion, the best way to design chips because no developer wants to waste time writing programs that take advantage of multiple thread capable CPUS - they rather the hardware figure it out. Its hard enough to use 2 out of 4 cores on a quad core now..imagine 32 cores!I wish they would give us a socket on the motherboards for a GPU chip. Then they can do multi-core cpus and multi-core dedicated gpus with new ultra fast buses to link. Plus I don't want Intel completly taking over all chip making...that would at the least cut out NVDIA who doesn't make CPUs. They backed the PS3 though so they might help push the Cell.

sprockkets - Friday, March 7, 2008 - link

Maybe Windows Mobile will now have a browser capable of doing IE5! No more excuses!Soccerman06 - Friday, March 7, 2008 - link

Can they throw on one socket? Would be interesting to see if you could put 32 on a socket and perform similar to core2 duo if the program was coded for that many cores.Janooo - Thursday, March 6, 2008 - link

Well, I'm just curious who's going to be the first with CPU and GPU on one silicon.