AMD Unveils Ryzen 9000 CPUs For Desktop, Zen 5 Takes Center Stage at Computex 2024

by Gavin Bonshor on June 2, 2024 11:00 PM EST- Posted in

- CPUs

- AMD

- Ryzen

- PCIe 5.0

- RDNA2

- N3

- Zen 5

- AM5

- Granite Ridge

- Computex 2024

- X870E

- X870

- TSMC N4

- Ryzen 9000

_678x452.jpg)

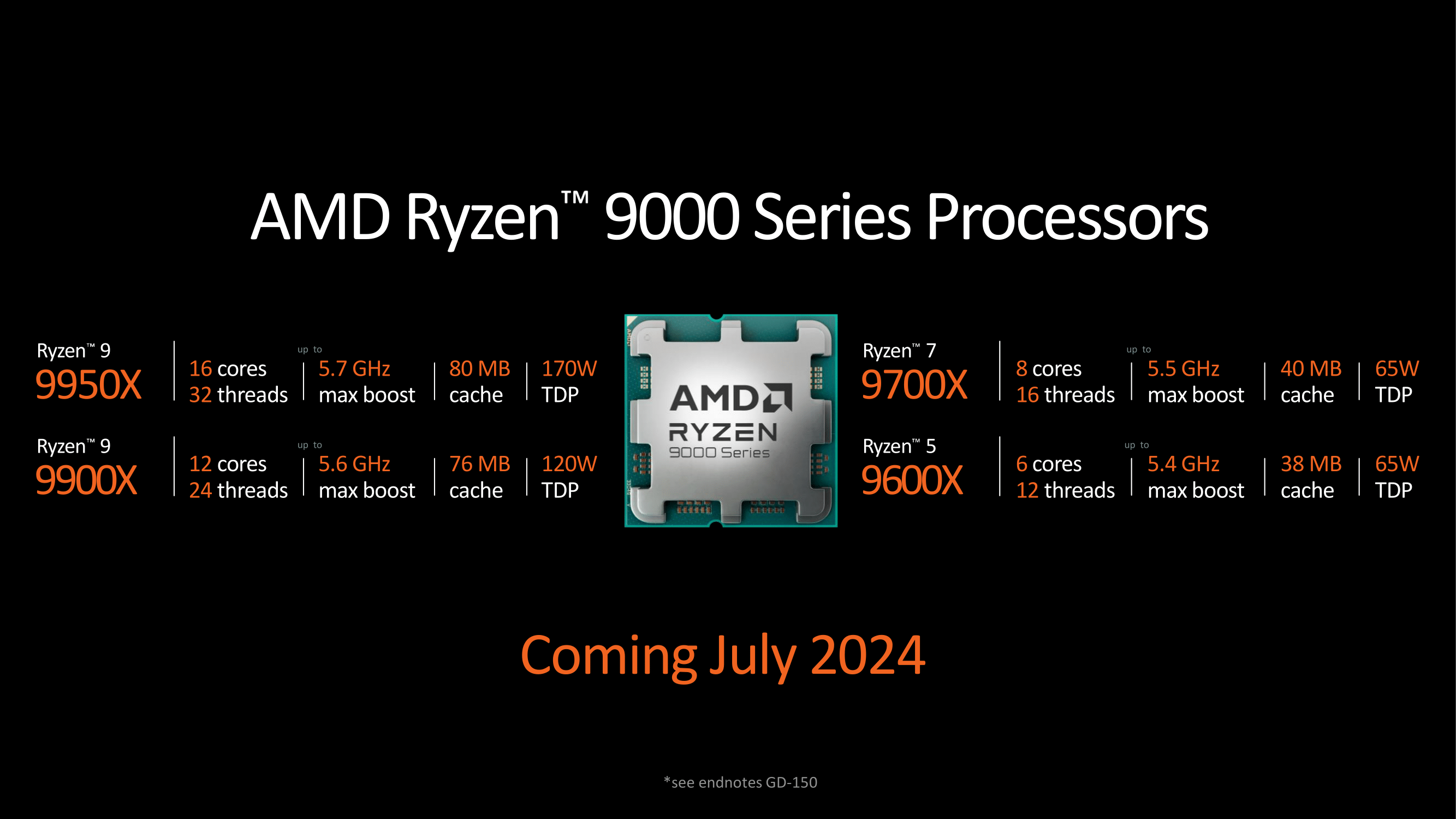

During AMD's Computex 2024 kick-off keynote, AMD's CEO, Dr. Lisa Su, officially unveiled and announced the company's next generation of Ryzen processors. Today marks the first unveiling of AMD's highly anticipated Zen 5 microarchitecture via the Ryzen 9000 series, which is set to bring several advancements over Zen 4 and the Ryzen 7000 series for desktop PCs, which will launch sometime in July 2024.

AMD has unveiled four new chip SKUs using its Zen 5 microarchitecture. The AMD Ryzen 9 9950X processor will be the new consumer flagship part, featuring 16 CPU cores and a speedy 5.7 GHz maximum boost frequency. The other SKUs include, 6, 8, and 12 core parts, giving users a varied combination of core and thread counts. All four of these initial chips will be X-series chips, meaning they will have an unlocked multipliers and higher TDPs/clockspeeds.

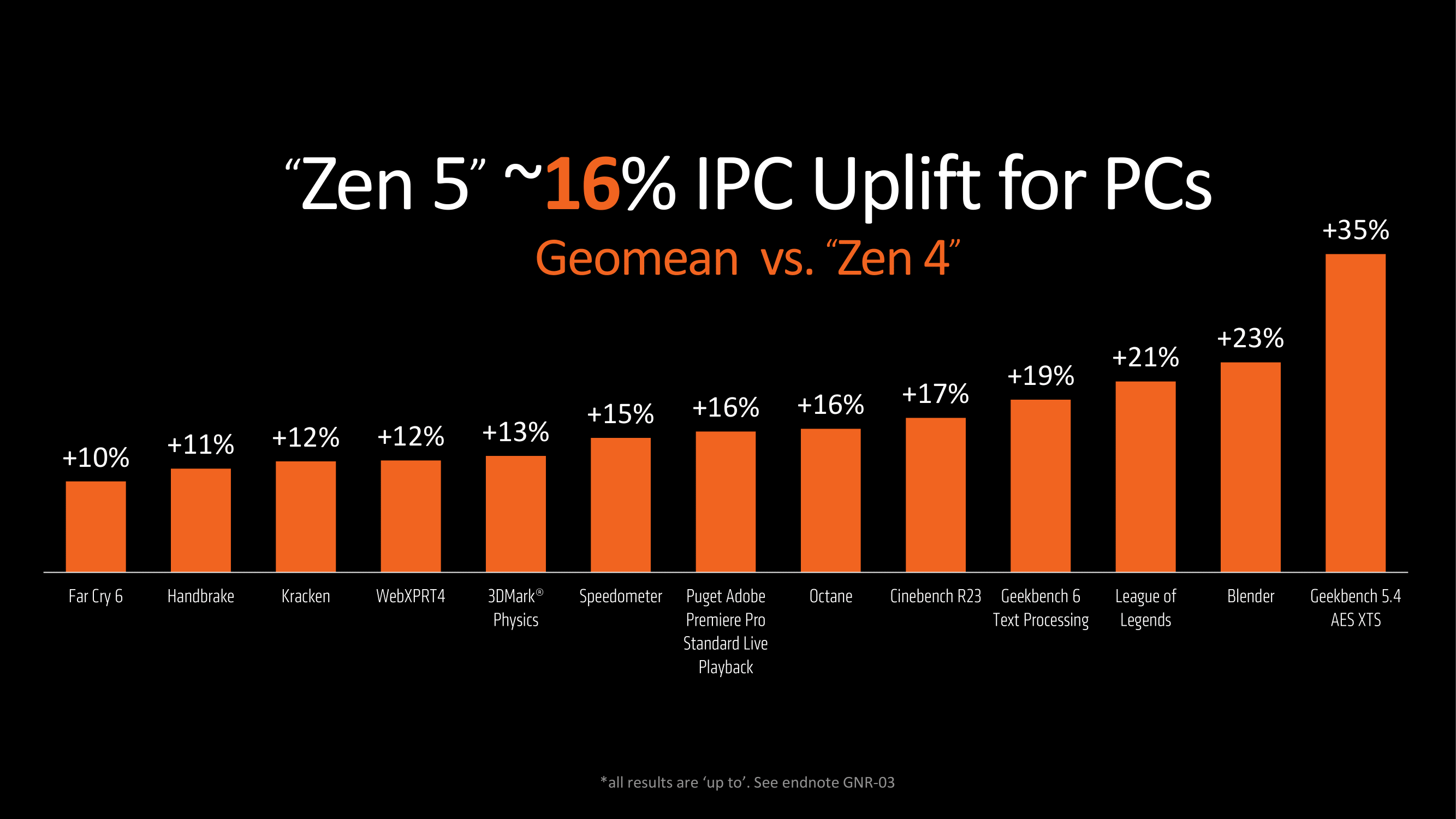

In regards to performance, AMD is touting an average (geomean) IPC increase in desktop workloads for Zen 5 of 16%. And with the new desktop Ryzen chips' turbo clockspeeds remaining largely identical to their Ryzen 7000 predecessors, this should translate into similar performance expectations for the new chips.

The AMD Ryzen 9000 series will also launch on the AM5 socket, which debuted with AMD's Ryzen 7000 series and marks AMD's commitment to socket/platform longevity. Along with the Ryzen 9000 series will come a pair of new high-performance chipsets: the X870E (Extreme) and the regular X870 chipsets. The fundamental features that vendors will integrate into their specific motherboards remain tight-lipped. Still, we do know that USB 4.0 ports are standard on the X870E/X870 boards, along with PCIe 5.0 for both PCIe graphics and NVMe storage, with higher AMD EXPO memory profile support expected than previous generations.

AMD Ryzen 9000: Bringing Up to 16C/32T of Zen 5 to Desktop

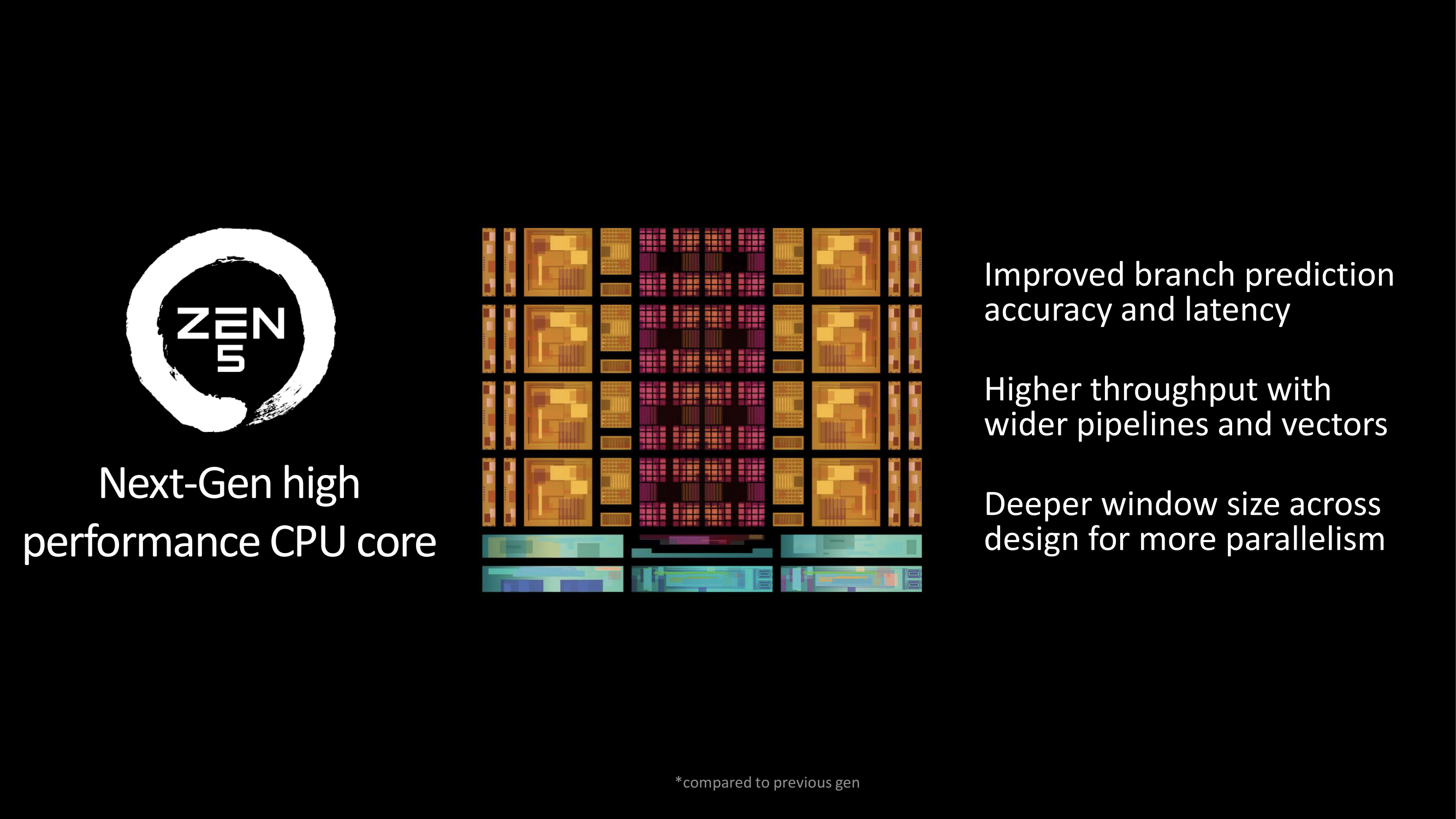

Zen 5 is AMD's latest advancement in Ryzen microarchitecture. While AMD hasn't disclosed many technical details, we know some of the brand-new features that Zen 5 will offer.

| AMD Desktop CPU Generations | |||

| AnandTech | Ryzen 9000 (Granite Ridge) |

Ryzen 7000 (Raphael) |

Ryzen 5000 (Vermeer) |

| CPU Architecture | Zen 5 | Zen 4 | Zen 3 |

| CPU Cores | Up to 16C / 32T | Up To 16C / 32T | Up To 16C / 32T |

| GPU Architecture | RDNA2 | RDNA2 | N/A |

| GPU Cores | 2 | 2 | N/A |

| Memory | DDR5-5600 | DDR5-5200 | DDR4-3200 |

| Platform | AM5 | AM5 | AM4 |

| CPU PCIe Lanes | 24x PCIe 5.0 | 24x PCIe 5.0 | 24x PCIe 4.0 |

| Manufacturing Process | CCD: TSMC N4 IOD:TSMC N6 |

CCD: TSMC N5 IOD: TSMC N6 |

CCD: TSMC N7 IOD: GloFo 12nm |

Looking at architectural differences between the last couple of generations (Zen 4 and Zen 3) and Zen 5, we know that AMD uses a new manufacturing process for its Ryzen 9000 desktop chips. While many have touted and speculated that Zen 5 for desktops will be built on one of TSMC's N3 (3 nm) nodes, some of our sources are saying that the Zen 5 CCD will be fabbed on TSMC N4 – though we are awaiting official confirmation about this (Update: And TSMC 4nm is now confirmed for the consumer Ryzen CCD). Furthermore, AMD's mobile counterpart offering, the Ryzen AI 300 series (Strix Point) has been confirmed for 4nm, and we've yet to see an AMD desktop CPU die produced on a more advanced node than its mobile counterpart.

While AMD is not offering a deep dive into the Zen 5 architecture at Computex, the company did touch upon a few of the major architectural improvements over Zen 4 that will be coming with the new CPU architecture. These start with an improved branch predictor, which is designed to offer better accuracy, efficiency, and reduced overall latency of instruction cycles. The Zen 5 architecture also boasts higher throughput with wider pipelines and SIMDs, allowing for faster data processing and equating to better overall performance in benchmarks such as CineBench and Blender and workloads leveraging the AVX-512 instruction set.

Additionally, Zen 5 introduces a deeper out-of-order instruction window size across its design, enabling more parallelism and better handling of multiple instructions within the pipeline simultaneously.

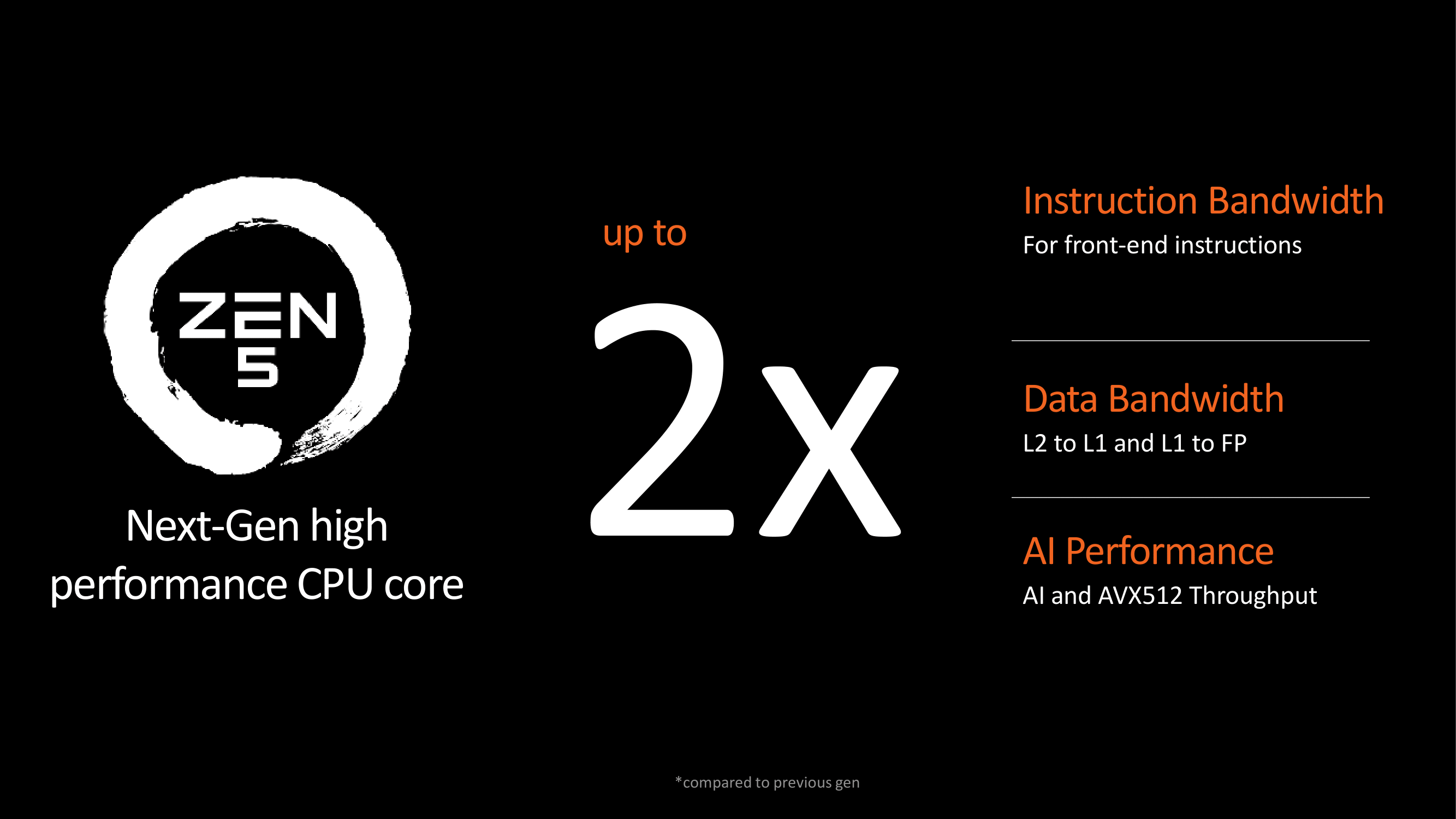

There are also a couple of points within the Zen 5 architecture where AMD has doubled up on resources or performance. L2 to L1 memory bandwidth is one such example, giving the cache hierarchy a big bandwidth boost that should allow for faster data transfers within the individual CPU cores. AMD also claims better AI performance in inferencing and AVX-512 workloads. Notably, AMD's AVX-512 support on Zen 4 was executed using a 256-bit SIMD over 2 cycles, so this may be a sign that AMD has expanded their AVX-512 SIMDs to a full 512-bits wide in the Zen 5 architecture. (Update: This has since been confirmed by AMD. Zen 5 now has a full 512-bit wide SIMD for processing AVX-512 instructions)

These enhancements collectively aim to deliver significant performance gains over the previous Zen 4 microarchitecture, with AMD touting an average (geomean) 16% IPC uplift over Zen 4 in desktop workloads. It should be noted, however, that the top result in this benchmark collection is in the GeekBench 5.3 AES XTS benchmark, which leverages the VAES512 and VAES256 extensions of the AVX-512 instruction set. So AMD's AVX-512 SIMD changes greatly impact that benchmark in particular (though not exclusively).

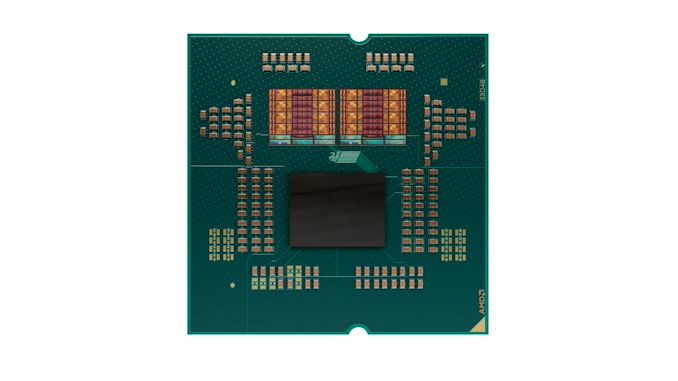

Above is a render of a Ryzen 9000 series chip with two core complex dies (CCDs), which depicts the silicon's composition and layout. As with previous generations of Ryzen processors, there's a large central I/O die (IOD), through which all I/O and memory operations are routed. As for the CCDs, each die once again contains 8 CPU cores, with AMD equipping Ryzen chips with either 1 or 2 CCDs depending on the SKU. The new Zen 5 CCDs are being fabbed on one of TSMC's 4nm processes (AMD hasn't confirmed which flavor), which is a modest shrink from the N5 process used for Zen 4 CCDs.

Meanwhile, although AMD hasn't confirmed that they're reusing the Ryzen 7000 series IOD here, all signs currently point to the Ryzen 9000 IOD being similar or identical to it. In particular, it is fabbed on the same TSMC N6 process, with the same 2 RDNA graphics CUs, and it offers the exact same off-chip I/O capabilities (though the latter is admittedly also dictated by the AM5 socket).

AMD's Ryzen 9000 chips will also feature similar memory support as their predecessors, with AMD sticking to DDR5. However, AMD does note that the incoming X870E and X870 motherboard chipsets will allow for faster EXPO memory profiles than seen on Zen 4. As it stands, AMD hasn't disclosed the JEDEC memory specification of the four Ryzen 9000 SKUs that it announced today. However, we expect to find out more before the July 2024 launch of the Ryzen 9000 family. And according to AMD's product pages posted since the keynote, the Ryzen 9000 family will top out at JEDEC DDR5-5600 speeds for in-warranty configurations.

| AMD Ryzen 9000 Series Processors Zen 5 Microarchitecture (Granite Ridge) |

|||||||

| AnandTech | Cores / Threads |

Base Freq |

Turbo Freq |

L2 Cache |

L3 Cache |

TDP | MSRP |

| Ryzen 9 9950X | 16C / 32T | 4.3GHz | 5.7GHz | 16 MB | 64 MB | 170 W | TBC |

| Ryzen 9 9900X | 12C / 24T | 4.4GHz | 5.6GHz | 12 MB | 64 MB | 120 W | TBC |

| Ryzen 7 9700X | 8C / 16T | 3.8GHz | 5.5GHz | 8 MB | 32 MB | 65 W | TBC |

| Ryzen 5 9600X | 6C / 12T | 3.9GHz | 5.4GHz | 6 MB | 32 MB | 65 W | TBC |

The announcement of Zen 5 for desktop by AMD and the impending Ryzen 9000 offers four X-series SKUs at launch, allowing for overclocking and coming with unlocked CPU multipliers. The flagship SKU, the Ryzen 9 9950X, features 16 cores, a max boost clock of up to 5.7 GHz, 80 MB of cache split between 64 MB for the L3 and 16 MB for the L2 (1 MB per core of L2) and a 170 W TDP. The Ryzen 9 9900X offers 12 cores, a max boost clock of up to 5.6 GHz, 64 MB of L3 cache, and a 120 W TDP.

Moving down the Ryzen 9000 stack is the Ryzen 7 9700X, which comes with 8 cores, a max boost clock of up to 5.5 GHz, 32 MB of L3 cache, and a 65W TDP. Finally, the entry-level SKU, the Ryzen 5 9600X, has just 6 cores, a max boost clock of up to 5.4 GHz, 32 MB of L3 cache, and a 65 W TDP.

The next slide denotes the flagship Zen 5 chip. The Ryzen 9 9950X is up against Intel's current 14th Gen Core i9-14900K. In productivity and content creation tasks, the Ryzen 9 9950X shows a 7% improvement in Procyon Office, a 10% increase in Puget Photoshop, and a 21% uplift in Cinebench R24 nT. More notably, it exhibits a 55% performance boost in Handbrake and a 56% increase in Blender.

Interestingly, the gaming data shows marginal gains in some titles, although it highlights more significant uplifts in others. AMD's in-house testing shows that the Ryzen 9 9950X outperforms the Intel Core i9-14900K by 4% in Borderlands 3, 6% in Hitman 3, and 13% in Cyberpunk 2077. Further, it achieves a 16% improvement in F1 2023, a 17% gain in DOTA 2, and a 23% increase in Horizon Zero Dawn.

As we've mentioned, AMD is committed to extending its AM5 socket for longevity, at least much more than other vendors offer with their CPU launches and updates. As such, AMD's Ryzen 9000 series operates on the current AM5 platform. And while Ryzen 9000 is fully backwards compatible with existing 600 series boards, AMD has also readied two new 800 series motherboard chipsets for the launch of Zen 5 on desktops. The X870E (extreme) and X870 chipsets will be featured on numerous new motherboards at launch, and a big part of Computex this week will be the motherboard vendors (most of whom are local Taiwanese firms) showing off their new wares.

AMD has offered just a handful of details about their X870E and X870 chipsets. Of particular note, USB 4.0 support is going to be standard on all X870(E) motherboards, whereas it was optional on X670(E) series boards. X870(E) boards will also feature Wi-Fi 7 support (up from 6E on the 600 series), and at least one PCIe 5.0 NVMe slot continues to be mandatory. AMD also notes that motherboards based on both platforms "feature 44 total PCIe lanes," which would break down as 24 lanes from the CPU, and another 20 lanes coming from the chipset.

| AMD AM5 Chipset Comparison | |||||

| Feature | X870E | X870 | X670E | X670 | B650E |

| CPU PCIe (PCIe) | 5.0 | 5.0 | 5.0 | 4.0 | 5.0 |

| CPU PCIe (M.2 Slots) | At Least 1 PCIe 5.0 Slot | ||||

| Total CPU PCIe Lanes | 24 | ||||

| Chipset PCIe Lanes (Max) | 4.0: 12 3.0: 8 |

4.0: 8 3.0: 4 |

4.0: 12 3.0: 8 |

4.0: 8 3.0: 4 |

|

| USB4 | Mandatory (Discrete, Consumes 4 Chipset PCie 4.0 Lanes) |

Optional | |||

| SATA Ports (Max) | 8 | 4 | 8 | 8 | 4 |

| DDR5 Support | Quad Channel (128-bit bus) | ||||

| Wi-Fi | Wi-Fi 7 (Discrete) | Wi-Fi 6E (Discrete) | |||

| CPU Overclocking Support | Yes | ||||

| Memory Overclocking Support | Yes | ||||

| # of Chips | 2 | 1 | 2 | 2 | 1 |

| Silicon | ASMedia Promontory 21 | ||||

| Available | July 2024 | July 2024 | Sept. 2022 | Sept. 2022 | Oct. 2022 |

For the moment, different AMD resources are in conflict with each other about PCIe 5.0 – or, at least, aren't being very clear about it. According to AMD's AM5 chipset page, both X870 and X870E feature PCie 5.0 for both the CPU NVMe lanes and CPU PEG lanes. However AMD's Compute press release states that X870E is "differentiated with 24 PCIe 5.0 lanes, with 16 lanes dedicated to graphics," implying that the vanilla X870 won't mandate PCIe 5.0 support. We're poking around AMD and the motherboard vendors to find out more.

Looking under the hood, AMD has confirmed that the new chipsets aren't based on new silicon. Instead, the company is using the same ASMedia-produced design as in the X670/B650 chipsets: the Promontory 21 controller. Given that the feature sets of the newer X870E/X870 motherboards are fundamentally similar to those of the X670E/X670 motherboards, aside from using newer external controllers such as Wi-Fi 7, there's apparently little need to change the chipset itself. Though given the lack of significant changes, it does raise the question of why AMD has skipped a generation in its nomenclature (700-series anyone?) and went straight to the 800-series chipset.

The AMD Ryzen 9000 series, including the flagship Ryzen 9 9950X (16C/32T), the Ryzen 9 9900X (12C/24T), the Ryzen 7 9700X (8C/16T), and the entry-level Ryzen 5 9600X (6C/12T) is expected to hit retail channels sometime in July 2024. At the time of writing, AMD is not providing pricing.

_thumb.png)

_thumb.png)

_thumb.png)

_thumb.png)

_thumb.png)

_thumb.png)

62 Comments

View All Comments

mode_13h - Friday, June 7, 2024 - link

> given that frequencies has decreased,Boost frequency limits stayed the same, except dropping 100 MHz on the 700X and 600X tiers. However, if the CPUs are better at maintaining boost, then we could see a *practical* increase in frequency!

You can't say it runs at lower frequencies until it's actually *tested*.

> looks like total performance stays about the same.

You're either very bad at math or a shameless troll. Reply

James5mith - Tuesday, June 4, 2024 - link

"And according to AMD's product pages posted since the keynote, the Ryzen 9000 family will top out at JEDEC DDR5-5600 speeds for in-warranty configurations."This sentence bothers me. Specifically, why create motherboards that support EXPO memory profiles if you don't plan on honoring the warranty for those motherboards if you use EXPO memory profiles? Reply

peevee - Tuesday, June 4, 2024 - link

So all the remains of Moore law are officially dead even for AMD, no improvements in 2 years. ReplyGeoffreyA - Wednesday, June 5, 2024 - link

The computer industry needs a breakthrough anyhow, beyond semiconductor and electrons. Replymode_13h - Friday, June 7, 2024 - link

peevee is just trolling. N4P is a quantifiably better node than N5 was. Replymode_13h - Friday, June 7, 2024 - link

TSMC claims 11% more performance, 22% higher power efficiency, and 6% higher transistor density over the N5 node.Some of that should translate into higher *practical* frequencies. Reply

peevee - Tuesday, June 4, 2024 - link

Does expanding the vector ALU also means ~doubling of AVX256 code performance/throughput? ReplyGeoffreyA - Wednesday, June 5, 2024 - link

It should, if the number of floating-point units remain the same or increase. Replymode_13h - Friday, June 7, 2024 - link

We don't yet know enough to say, however I'm not hopeful because their slide specifically said "2x AI and AVX-512 throughput", rather than a broader statement that you'd expect to see if it also applied to 256-bit operands. ReplyBruzzone - Wednesday, June 5, 2024 - link

5900XT and 5800XT on AMD so said pricing is sufficient to push Vermeer channel holdings down in price at so said $359 and $249 now pulled by AMD in the moment. The channel might not have been happy with that regulating price move on how much R5K there is too clear from the channel. R5K channel available is up + 68% since March 9 when R5K was 68% of all R7K and today 98% of R7K available.R7K desktop since March 9 channel supply volume available + 18%. R9K will minimally dribble out allowing R7K and R5K to clear? R9K might have to be priced up on specific SKUs to accomplish the same dribbling out objective allowing AMD back generation to clear?

Notably 3600 gains in the channel + 94% in the prior month.

3600X came back to secondary resale + 35%.

3700X is up + 15.8% that's all trade-in.

AMD might have to adjust R9K desktop top SKU and R5K desktop regulating SKUs not to interfere with the channel's ability to liquidate especially Vermeer from channel inventory holdings plus R7K SKUs that will follow in a first in first out channel sales system.

In summary, there is plenty of Intel and AMD product in the channel. The PC market remains in a downward deflationary price spiral until at least q1 2025 aimed to clear existing inventories for channel financial reclaim to buy next generation.

Subsequently there's this inventory bridge to traverse to Intel and AMD next generation products and through the summer into q4 it's never been a better time to buy a PC. I don't think desktop and mobile prices will be as low as they are heading into year end and for a long time following.

mb Reply