AMD Zen Architecture Roadmap: Zen 5 in 2024 With All-New Microarchitecture

by Ryan Smith on June 9, 2022 4:21 PM EST

Today is AMD’s Financial Analyst Day, the company’s semi-annual, analyst-focused gathering. While the primary purpose of the event is for AMD to reach out to investors, analysts, and others to demonstrate the performance of the company and why they should continue to invest in the company, FAD has also become AMD’s de-facto product roadmap event. After all, how can you wisely invest in AMD if you don’t know what’s coming next?

As a result, the half-day series of presentations is full of small nuggets of information about products and plans across the company. Everything here is high-level – don’t expect AMD to hand out the Zen 4 transistor floorplan – but it’s easily our best look at AMD’s product plans for the next couple of years.

Kicking off FAD 2022 with what’s always AMD’s most interesting update is the Zen architecture roadmap. The cornerstone of AMD’s recovery and resurgence into a competitive and capable player in the x86 processor space, the Zen architecture is the basis of everything from AMD’s smallest embedded CPUs to their largest enterprise chips. So what’s coming down the pipe over the next couple of years is a very big deal for AMD, and the industry as a whole.

Zen 4: Improving Performance and Perf-Per-Watt, Shipping Later This Year

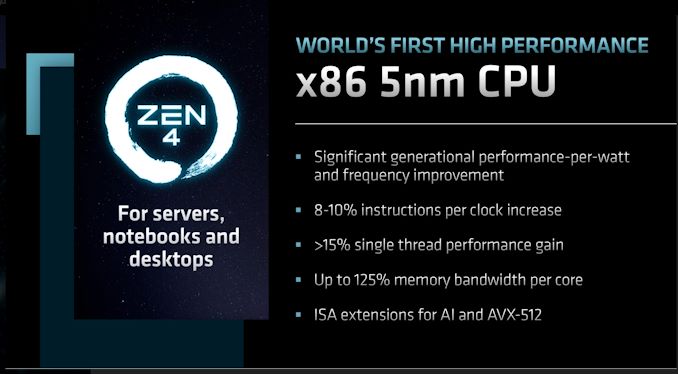

Diving right in, AMD is currently in the process of ramping up their Zen 4 architecture-based products. This includes the Ryzen 7000 (Raphael) client CPUs, as well as their 4th generation EPYC (Genoa) server CPUs. Both of these are due to launch later this year.

We’ve seen bits and pieces of information on Zen 4 thus far, most recently with the Ryzen 7000 announcement at Computex. Zen 4 brings new CPU core chiplets as well as a new I/O die, adding support for features such as PCI-Express 5.0 and DDR5 memory. And on the performance front, AMD is aiming for significant performance-per-watt and clockspeed improvements over their current Zen 3-based products.

Meanwhile, AMD is following up that Computex announcement by clarifying a few things. In particular, the company is addressing questions around Instruction per Clock (IPC) expectations, stating that they expect Zen 4 to offer an 8-10% IPC uplift over Zen 3. The initial Computex announcement and demo seemed to imply that most of AMD’s performance gains were from clockspeed improvements, so AMD is working to respond to that without showing too much of their hand months out from the product launches.

Coupled with that, AMD is also disclosing that they’re expecting an overall single-threaded performance gain of greater than 15% – with an emphasis on “greater than.” ST performance is a mix of IPC and clockspeeds, so at this point AMD can’t get overly specific since they haven’t locked down final clockspeeds. But as we’ve seen with their Computex demos, for lightly threaded workloads, 5.5GHz (or more) is currently on the table for Zen 4.

Finally, AMD is also confirming that there are ISA extensions for AI and AVX-512 coming for Zen 4. At this point the company isn’t clarifying whether either (or both) of those extensions will be in all Zen 4 products or just a subset – AVX-512 is a bit of a space and power hog, for example – but at a minimum, it’s reasonable to expect these to show up in Zen 4 server parts. The addition of AI instructions will help AMD keep up with Intel and other competitors in the short run, as CPU AI performance has already become a battleground for chipmakers. Though just what this does for AMD’s competitiveness there will depend in large part on just what instructions (and data types) get added.

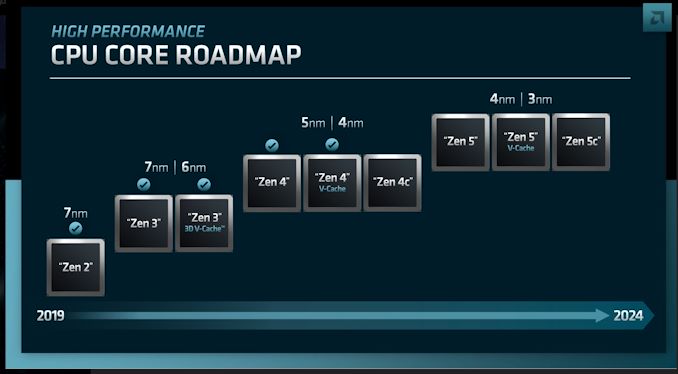

AMD will be producing three flavors of Zen 4 products. This includes the vanilla Zen 4 core, as well as the previously-announced Zen 4c core – a compact core that is for high density servers and will be going into the 128 core EPYC Bergamo processor. AMD is also confirming for the first time that there will be V-Cache equipped Zen 4 parts as well – which although new information, does not come as a surprise given the success of AMD’s V-Cache consumer and server parts.

Interestingly, AMD is planning on using both 5nm and 4nm processes for the Zen 4 family. We already know that Ryzen 7000 and Genoa are slated to use one of TSMC’s 5nm processes, and that Zen 4c chiplets are set to be built on the HPC version of N5. So it’s not immediately clear where 4nm fits into AMD’s roadmap, though we can’t rule out that AMD is playing a bit fast and loose with terminology here, since TSMC’s 4nm processes are an offshoot of 5nm (rather than a wholly new node) and are typically classified as 5nm variants to start with.

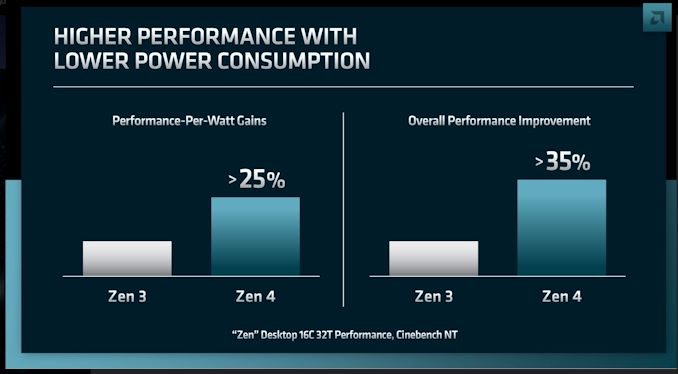

At this point, AMD is expecting to see a >25% increase in performance-per-watt with Zen 4 over Zen 3 (based on desktop 16C chips running CineBench). Meanwhile the overall performance improvement stands at >35%, no doubt taking advantage of both the greater performance of the architecture per-thread, and AMD’s previously disclosed higher TDPs (which are especially handy for uncorking more performance in MT workloads). And yes, these are terrible graphs.

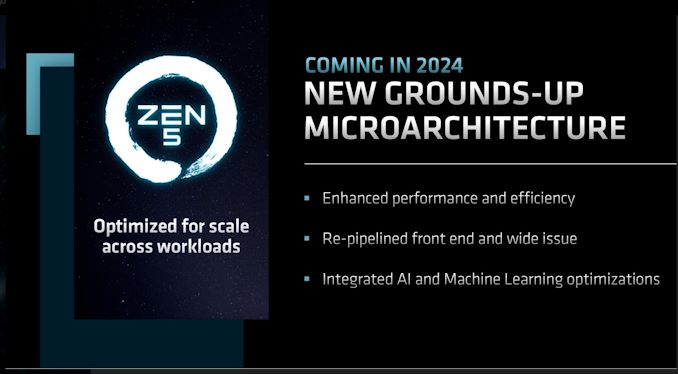

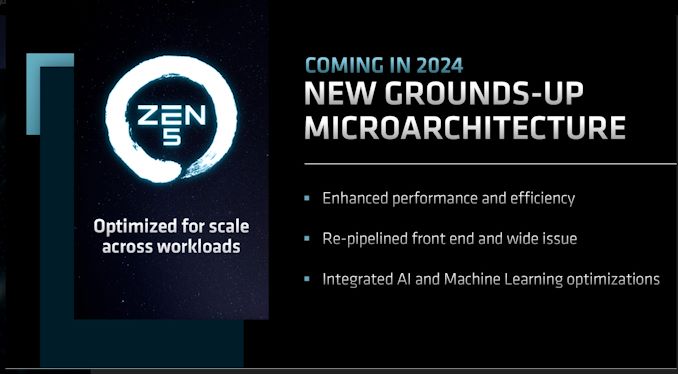

Zen 5 Architecture: All-New Microarchitecture for 2024

Meanwhile, carrying AMD’s Zen architecture roadmap into 2024 is the Zen 5 architecture, which is being announced today. Given that AMD isn’t yet shipping Zen 4, their details on Zen 5 are understandably at a very high level. None the less, they also indicate that AMD won’t be resting on their laurels, and have some aggressive updates planned.

The big news here is that AMD is terming the Zen 5 architecture as an “All-new microarchitecture”. Which is to say, it’s not merely going to be an incremental improvement over Zen 4.

In practice, no major vendor designs a CPU architecture completely from scratch – there’s always going to be something good enough for reuse – but the message from AMD is clear: they’re going to be doing some significant reworking of their core CPU architecture in order to further improve their performance as well as energy efficiency.

As for what AMD will disclose for right now, Zen 5 will be re-pipelining the front end and once again increasing their issue width. The devil is in the details here, but coming from Zen 3 and its 4 instruction/cycle decode rate, it’s easy to see why AMD would want to focus on that next – especially when on the backend, the integer units already have a 10-wide issue width.

Meanwhile, on top of Zen 4’s new AI instructions, Zen 5 is integrating further AI and machine learning optimizations. AMD isn’t saying much else here, but they have a significant library of tools to pick from, covering everything from AI-focused instructions to adding support for even more data types.

AMD expects the Zen 5 chip stack to be similar to Zen 4 – which is to say that they’re going to have the same trio of designs: a vanilla Zen 5 core, a compact core (Zen 5c), and a V-Cache enabled core. For AMD’s customers this kind of continuity is very important, as it gives customers a guarantee that AMD’s more bespoke configurations (Zen 4c & V-Cache) will have successors in the 2024+ timeframe. From a technical perspective none of this is too surprising, but from a business standpoint, customers want to make sure they aren’t adopting dead-end hardware.

Finally, AMD has an interesting manufacturing mix planned for Zen 5. Zen 5 CPU cores will be fabbed on a mix of 4nm and 3nm processes, which unlike the 5nm/4nm mix for Zen 4, TSMC’s 4nm and 3nm nodes are very different. 4nm is an optimized version of 5nm, whereas 3nm is a whole new node. So if AMD’s manufacturing plans move ahead as currently laid out, Zen 5 will be straddling a major node jump. That said, it’s not unreasonable to suspect that AMD is hedging their bets here and leaving 4nm on the table in case 3nm isn’t as far along as they’d like.

Wrapping things up, the Zen 5 architecture is slated for 2024. AMD isn’t giving any further information on when in the year that might be, though looking at Zen 3 and Zen 4, both of those were/will be released later on in 2020 and 2022 respectively. So H2/EOY 2024 is as good as guess as any.

156 Comments

View All Comments

lemurbutton - Friday, June 10, 2022 - link

I expect AMD to finally match M1's perf/watt when it's Zen6 and using second-gen 3nm.By then, Apple will be on M5 using 2nm.

BushLin - Saturday, June 11, 2022 - link

The 15w M1 was trading blows with the already launched 15w Renoir (Zen 2) in 2020.https://www.anandtech.com/show/16252/mac-mini-appl...

Fantastic claims require fantastic evidence and I've not seen anything that comes close to backing up any of what you're claiming.

Qasar - Saturday, June 11, 2022 - link

BushLin, he cant, cause he knows his posts are bs, and just fanboy postsdr.denton - Friday, June 10, 2022 - link

lol, who cares about Apple? They have 9% market share on desktop and 15% in laptops. Everything else is x86.Would an M1 equipped Macbook be amazing if it could run all my stuff natively (including thousands of indie games) and I had 2000€ to spare? Sure. But for most people those are BIG ifs.

Speedfriend - Friday, June 10, 2022 - link

Who cares about Apple....? It is not Apple that is the issue for AMD and Intel, it is Qualcomm and what they can do with Nuvia. If that is competitive with M2 in terms of performance and efficiency when it launches, there is going to be a shift to Windows on ARM. My high powered x86 laptop is a total joke on battery, it can barely last a 2 hour meeting, let alone a conference. Ill be switching as soon as possibleKangal - Friday, June 10, 2022 - link

Qualcomm is run by some greedy corporate types, and most of their talented designers have left the company a few years ago. The Nuvia cores did look promising and they were supposed to be released ages ago, until Qualcomm basically bought them out.I just don't expect much to come from Qualcomm-Windows. You are better off sticking with Android instead for the Efficiency, UI, and Apps. Or if you need proper Windows, stick with the x86_64 platform instead of an emulated-environment.

OreoCookie - Friday, June 10, 2022 - link

Intel and AMD do, for one. Apple shows what a good architecture can do in terms of performance, performance-per-watt, dedicated logic and what trends are. Intel referenced Apple‘s M1 specifically in internal slides as what they are shooting for (some years later).I expect that Apple‘s decision to dramatically increase memory bandwidth will have an impact on AMD‘s and Intel‘s decisions as well. Even the M2 (without modifier) has 100 GB/s memory bandwidth, which is close to what AnandTech measured in AMD’s Milan. (I realize I compare theoretical maximums with actually measured throughputs, but my point is more about where to put the emphasis in design.) And it stands to reason that the M2 Pro/Max/Ultra will at least match the M1 variants.

BushLin - Saturday, June 11, 2022 - link

If the 100GB/s bandwidth figure is anything like what was marketed on the M1 Max then only a fraction of that is available to the CPU cores.M1 Max headline number from Apple is 400GB/s but the reality is 100GB/s single threaded and <250GB/s best case scenario with all cores loaded.

https://www.anandtech.com/show/17024/apple-m1-max-...

Not saying the performance numbers won't be impressive for a little SoC but far from the Jesus silicon some fantasize might about.

Not aimed at the poster above but it helps to post links with actual results rather than slinging around far fetched claims.

OreoCookie - Saturday, June 11, 2022 - link

Fair point, and I should have mentioned that.However, my point was two-fold: my comparison to measurements in Milan was to make the point that Apple decided to spend silicon to give the M2 — Apple’s smallest non-iPhone SoC — roughly the same type of memory bandwidth as a server-class x86 CPU — or way more in case of the Mx modifier variants. So rather than spending more transistors and power optimizing the CPU, Apple dedicates them to memory and caches.

And secondly, the large increase in bandwidth means that memory bandwidth is not a bottleneck for total performance (true at least for the M1 Max and M1 Ultra, because even when CPU, GPU and other specialized logic is running full tilt, the SoC still has enough memory bandwidth to saturate them all). The same cannot be said for many of AMD‘s and Intel‘s CPUs (at least the ones with higher core counts and/or integrated GPUs).

My prediction is that Intel and AMD will follow suit in the future and give more emphasis to memory bandwidth, i. e. Apple‘s SoCs definitely do influence what Intel and AMD are doing — which is what I was replying to. You can also see that Intel and AMD are trying to integrate more specialized circuitry for specialized tasks as well, also something that Apple has emphasized (in terms of transistors and power) on its M-series SoCs.

mode_13h - Sunday, June 12, 2022 - link

> roughly the same type of memory bandwidth as a server-class x86 CPUNot at all. It's only workstation-class. EPYC Milan and last year's Ice Lake SP both have 8-channel DDR4, providing nominal bandwidth of 204.8 GB/s. Cut that in half and you get something like Threadripper (non-Pro) bandwidth numbers.

DDR5, with Sapphire Rapids shipping probably around the same time as M2-based systems, will move the bar yet again. With it, even desktop platforms are creeping into M2 territory. Alder Lake has a nominal bandwidth of 76.8 GB/s.

So, Apple is really only barely keeping pace, considering graphics needs a share of that bandwidth. For perspective, the PS4 that launched almost 9 years ago had 176 GB/s unified memory bandwidth.

You need to get with the times.