Intel Architecture Day 2021: Alder Lake, Golden Cove, and Gracemont Detailed

by Dr. Ian Cutress & Andrei Frumusanu on August 19, 2021 9:00 AM EST

This week Intel held its annual Architecture Day event for select press and partners. As with previous iterations, the company disclosed details about its next generation architectures set to come to the market over the next twelve months. Intel has promised the release of its next-generation consumer and mobile processor family, Alder Lake, to come by the end of the year and today the company is sharing a good number of details about the holistic design of the chips as well as some good detail about the microarchitectures that form this hybrid design: Golden Cove and Gracemont. Here is our analysis of Intel’s disclosure.

Alder Lake: Intel 12th Gen Core

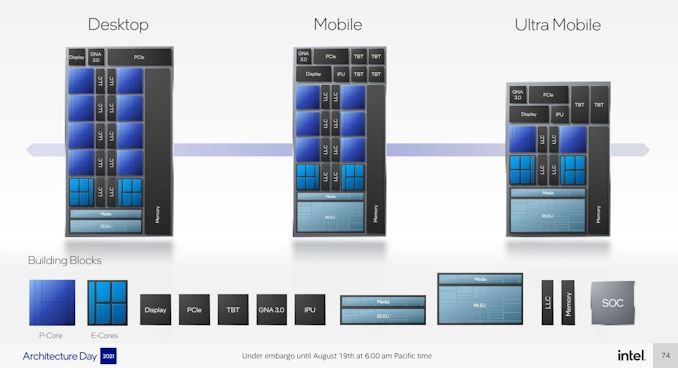

As mentioned in previous announcements, Intel will launch its Alder Lake family of processors into both desktop and mobile platforms under the name of Intel’s 12th Gen Core Processors with Hybrid Technology later this year. This is Intel’s second generation hybrid architecture built on Intel 7 process node technology. The hybrid design follows Intel Lakefield designs for small notebooks launched last year. The nature of a hybrid design in Intel nomenclature involves having a series of high ‘Performance’ cores paired with a number of high ‘Efficiency’ cores. Intel has simplified this into P-core and E-core terminology.

For Alder Lake, the processor designs feature Performance cores based on a new Golden Cove microarchitecture, and Efficiency cores based on a new Gracemont architecture. We will cover both over the course of this article, however the idea is that the P-core is preferential for single threaded tasks that require low latency, and the E-core is better in power limited or multi-threaded scenarios. Each Alder Lake SoC will physically contain both, however Intel has not yet disclosed the end-user product configurations.

Each of the P-cores has the potential to offer multithreading, whereas the E-cores are one thread per core. This means there will be three physical designs based on Alder Lake:

- 8 P-core + 8 E-core (8C8c/24T) for desktop on a new LGA1700 socket

- 6 P-core + 8 E-core (6C8c/20T) for mobile UP3 designs

- 2 P-core + 8 E-core (2C8c/12T) for mobile UP4 designs

Intel typically highlights UP4 mobile designs for very low power installs, down to 9 W, whereas UP3 can cover anything from 12 W to 35 W (or perhaps higher), but when asked about the power budgets for these processors, Intel stated that more detail will follow when product announcements are made. Intel did confirm that the highest client power, presumably on the desktop processor, will be 125 W.

Highlighted in our discussions is how modular Intel has made Alder Lake. From a range of base component options, the company mixed and matched what it felt were the best combination of parts for each market.

Here it shows that four E-cores takes up the same physical space as one P-core, but also that the desktop hardware will at most have 32 EUs (Execution Units) for Xe-LP graphics (same as the previous generation), while both of the mobile processors will offer 96 physical EUs that may be disabled down based on the specific line item in the product stack.

All three processors will feature Intel’s next generation Gaussian Neural Accelerator (GNA 3.0) for minor low power AI tasks, a display engine, and some level of PCIe, however the desktop processor will have more. Only the mobile processors will get an Image Processing Unit (IPU), and Thunderbolt 4 (TBT), and here the big UP3 mobile processor gets four ports of Thunderbolt whereas the smaller UP4 will only get two. The desktop processor will not have any native Thunderbolt connectivity.

A bit more info on the Desktop Processor IO and Interconnect

We’ll cover a bit more detail about the core designs later in this article, but Intel did showcase some of the information on the desktop processor. It confirmed explicitly that there would be 16 total cores and 24 threads, with up to 30 MB of non-inclusive last level/L3 cache.

In contrast to previous iterations of Intel’s processors, the desktop processor will support all modern standards: DDR5 at 4800 MT/s, DDR4-3200, LPDDR5-5200, and LPDDR4X-4266. Alongside this the processor will enable dynamic voltage-frequency scaling (aka turbo) and offer enhanced overclocking support. What exactly that last element means we’re unclear of at this point.

Intel confirmed that there will not be separate core designs with different memory support – all desktop processors will have a memory controller that can do all four standards. What this means is that we may see motherboards with built-in LPDDR5 or LPDDR4X rather than memory slots if a vendor wants to use LP memory, mostly likely in integrated small form factor designs but I wouldn’t put it past someone like ASRock to offer a mini-ITX board with built in LPDDR5. It was not disclosed what memory architectures the mobile processors will support, although we do expect almost identical support.

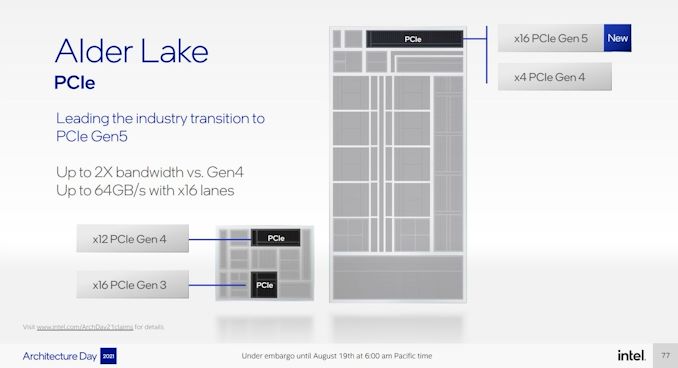

On the PCIe side of things, Alder Lake’s desktop processor will be supporting 20 lanes of PCIe, and this is split between PCIe 4.0 and PCIe 5.0.

The desktop processor will have sixteen lanes of PCIe 5.0, which we expect to be split as x16 for graphics or as x8 for graphics and x4/x4 for storage. This will enable a full 64 GB/s bandwidth. Above and beyond this are another four PCIe 4.0 lanes for more storage. As PCIe 5.0 NVMe drives come to market, users may have to decide if they want the full PCIe 5.0 to the discrete graphics card or not

Intel also let it be known that the top chipset for Alder Lake on desktop now supports 12 lanes of PCIe 4.0 and 16 lanes of PCIe 3.0. This will allow for additional PCIe 4.0 devices to use the chipset, reducing the number of lanes needed for items like 10 gigabit Ethernet controllers or anything a bit spicier. If you ever thought your RGB controller could use more bandwidth, Intel is only happy to provide.

Intel did not disclose the bandwidth connectivity between the CPU and the chipset, though we believe this to be at least PCIe 4.0 x4 equivalent, if not higher.

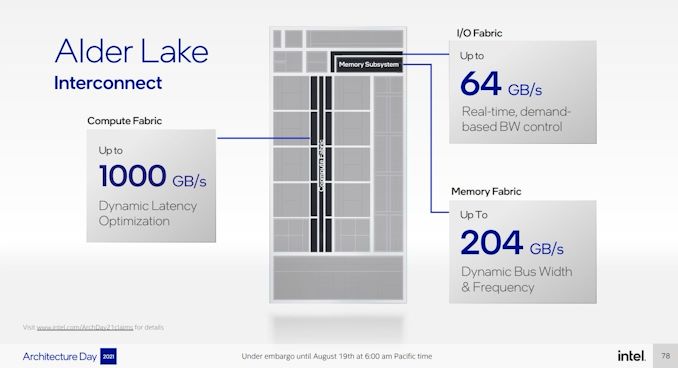

The Alder Lake processor retains the dual-bandwidth ring we saw implemented in Tiger Lake, enabling 1000 GB/s of bandwidth. We learned from asking Intel in our Q&A that this ring is fully enabled regardless of whether the P-cores or E-cores are being used – Intel can disable one of the two rings when less bandwidth is needed, which would save power, however based on previous testing this single ring could end up drawing substantial power compared to the E-cores in low power operation. (This may be true in the mobile processors as well, which would have knock on effects for mobile battery life.)

The 64 GB/s of IO fabric is in line with the PCIe 5.0 x16 numbers we saw above, however the 204 GB/s of memory fabric bandwidth is a confusing number. Alder Lake features a 128-bit memory bus, which allows for 4x 32-bit DDR5 channels (DDR5 has two 32-bit channels per module, so 2 modules still), however in order to reach 204 GB/s in that configuration requires DDR5-12750; Intel has rated the processor only at DDR5-4800, less than half that, so it is unclear where this 204 GB/s number comes from. For perspective, Intel’s Ice Lake does 204.8 GB/s, and that’s a high-power server platform with 8 channels of DDR4-3200.

This final slide mentions TB4 and Wi-Fi 6E, however as with previous desktop processors, these are derived from controllers attached to the chipset, and not in the silicon itself. The mobile processors will have TBT integrated, but the desktop processor does not.

This slide also mentions Intel Thread Director, which we want to address on the next page before we get to the microarchitecture analysis.

223 Comments

View All Comments

Unashamed_unoriginal_username_x86 - Thursday, August 19, 2021 - link

When you say "similar in magnitude to what skylake did" on the Golden Cove page, are you sure you don't mean something like Sandy Bridge? I vaguely remember Skylake being a pretty nominal improvement on the order of 10-15%mode_13h - Thursday, August 19, 2021 - link

> I vaguely remember Skylake being a pretty nominal improvement on the order of 10-15%That would NOT be a nominal improvement! Fortunately, the real number isn't hard to find:

https://www.anandtech.com/show/9483/intel-skylake-...

"In our IPC testing, ... we saw a 5.7% increase in performance over Haswell. That value masks the fact that between Haswell and Skylake, we have Broadwell, marking a 5.7% increase for a two generation gap."

"In our discrete gaming benchmarks, at 3GHz Skylake actually performs worse than Haswell at an equivalent clockspeed, giving up an average of 1.3% performance."

Wereweeb - Thursday, August 19, 2021 - link

Funny how Ryzen made people used to thinking in terms of generational improvements as "10-15%" again. Thankfully, EUV and GAAFETs will make sure the next few generations keep advancing at that pace.mode_13h - Thursday, August 19, 2021 - link

> are you sure you don't mean something like Sandy Bridge?Exactly. The timeframe of "a decade" and the magnitude of the changes they're describing lines up with Sandybridge.

Spunjji - Monday, August 23, 2021 - link

Definitely referring to Sandy Bridge, as that was a 2011 architecture.zzzxtreme - Thursday, August 19, 2021 - link

been waiting 10 years for this, assuming this is a breakthrough x86 cpucheshirster - Thursday, August 19, 2021 - link

Not this time.shabby - Thursday, August 19, 2021 - link

Finally we'll see how good intels 10nm is...AdrianBc - Thursday, August 19, 2021 - link

"E-core will be at ‘Haswell-level’ AVX2 support" seems to be contradicted by the slides from the Intel presentation, which imply that Gracemont does not have FMA, but only separate FADD and FMUL.If the Intel slides are correct Gracemont cannot support the complete Haswell instruction set.

Maybe Gracemont supports only the 256-bit integer instructions added by Haswell over Sandy Bridge and it might also not support the BMI Haswell instructions.

Also weird is that the original Intel presentation does not contain the terms AVX or AVX2, but only some vague "support for Advanced Vector Instructions".

So, unless Intel has purposedly confused the presentations for now, it looks like the Gracemont and Golden Cove do not have compatible instructions sets, even with AVX-512 disabled.

If that is true, then disabling AVX-512 must have only one reason, decreasing the manufacturing cost for Alder Lake, by using all the defect chips and reserving the good ones for Sapphire Rapids.

AdrianBc - Thursday, August 19, 2021 - link

After writing the comment above, I have looked again at the Gracemont presentation and only now I have noticed that in the same slide that does not show any FMA unit it is written that it indeed supports the FMA instructions.I do not know why 2 FADD + 2 FMUL are shown instead of 2 FMA, like in the slide for Golden Cove.

Because each FADD is on the same port with an FMUL, this means that Gracemont cannot function like AMD Zen, which can do an extra separate FADD besides an FMUL, when the full FMA is not needed. If the FMA and the FMUL cannot be executed simultaneously, then they should have drawn it as just an FMA unit, like in the Golden Cove slide.

In any case even if Gracemont would be compatible with Haswell + the SHA extension, that still cannot make it instruction compatible with Golden Cove, because there are important additional instructions introduced in Broadwell, Ice Lake and Tiger Lake.