Update: PCI Express 6.0 Draft 0.71 Released, Final Release by End of Year

by Ryan Smith on July 2, 2021 7:00 AM EST- Posted in

- CPUs

- Interconnect

- PCIe

- PCI-SIG

- PCIe 6.0

Update 07/02: Albeit a couple of days later than expected, the PCI-SIG has announced this morning that the PCI Express draft 0.71 specification has been released for member review. Following a minimum 30 day review process, the group will be able to publish the draft 0.9 version of the specficiation, putting them on schedule to release the final version of the spec this year.

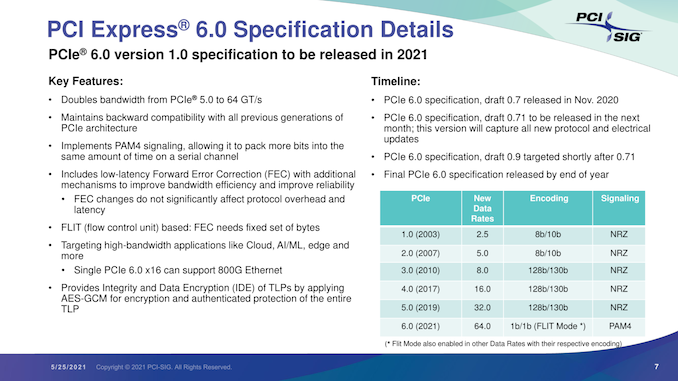

Originally Published 05/25

As part of their yearly developer conference, the PCI Special Interest Group (PCI-SIG) also held their annual press briefing today, offering an update on the state of the organization and its standards. The star of the show, of course, was PCI Express 6.0, the upcoming update to the bus standard that will once again double its data transfer rate. PCI-SIG has been working on PCIe 6.0 for a couple of years now, and in a brief update, confirmed that the group remains on track to release the final version of the specification by the end of this year.

The most recent draft version of the specification, 0.7, was released back in November. Since then, PCI-SIG has remained at work collecting feedback from its members, and is gearing up to release another draft update next month. That draft will incorporate the all of the new protocol and electrical updates that have been approved for the spec since 0.7.

In a bit of a departure from the usual workflow for the group, however, this upcoming draft will be 0.71, meaning that PCIe 6.0 will be remaining at draft 0.7x status for a little while longer. The substance of this decision being that the group is essentially going to hold for another round of review and testing before finally clearing the spec to move on to the next major draft. Overall, the group’s rules call for a 30-day review period for the 0.71 draft, after which the group will be able to release the final draft 0.9 specification.

Ultimately, all of this is to say that PCIe 6.0 remains on track for its previously-scheduled 2021 release. After draft 0.9 lands, there will be a further two-month review for any final issues (primarily legal), and, assuming the standard clears that check, PCI-SIG will be able to issue the final, 1.0 version of the PCIe 6.0 specification.

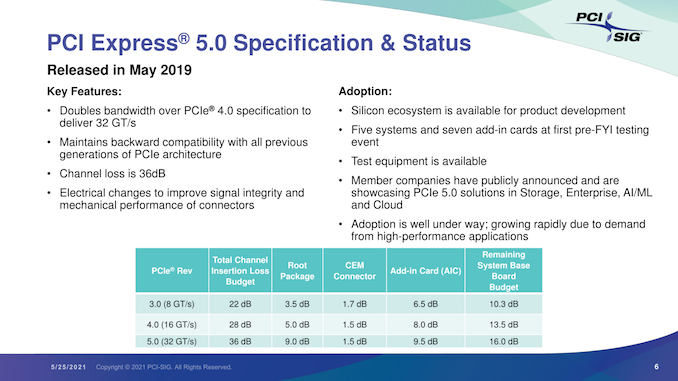

In the interim, the 0.9 specification is likely to be the most interesting from a technical perspective. Once the updated electrical and protocol specs are approved, the group will be able to give some clearer guidance on the signal integrity requirements for PCIe 6.0. All told we’re not expecting much different from 5.0 (in other words, only a slot or two on most consumer motherboards), but as each successive generation ratchets up the signaling rate, the signal integrity requirements have tightened.

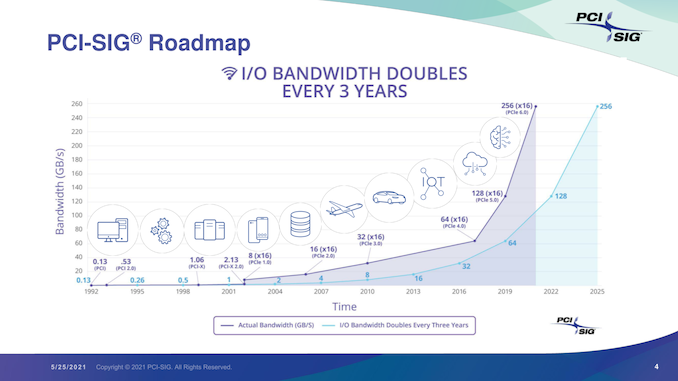

Overall, the unabashedly nerdy standards group is excited about the 6.0 standard, comparing it in significance to the big jump from PCIe 2.0 to PCIe 3.0. Besides proving that they’re once again able to double the bandwidth of the ubiquitous bus, it will mean that they’ve been able to keep to their goal of a three-year cadence. Meanwhile, as the PCIe 6.0 specification reaches completion, we should finally begin seeing the first PCIe 5.0 devices show up in the enterprise market.

103 Comments

View All Comments

melgross - Wednesday, May 26, 2021 - link

None of that matters today. It’s an interesting historical line that I remember quite well. It also has little to do with what’s being done today.As far as consumers go, it’s all about price, at least for Window’s and Chrome users are concerned. That’s a fast race to the bottom.

Yojimbo - Thursday, May 27, 2021 - link

If it doesn't matter why do they put the "doubling every three years" graph there?rahvin - Tuesday, May 25, 2021 - link

We got PCIE 1.0 devices so quickly because of the all the work done leading up to it and more importantly how inadequate PCI, AGP and VESA were. No subsequent upgrade since 1.0 has arrived that quickly. PCIE3 was out for a few years before the first devices arrived and 4 was even worse. I expect the first 5.0 MB's and devices will be next year or 2023 and 6.0 production devices is a long way away.Matthias B V - Wednesday, May 26, 2021 - link

Well first PCIe 5.0 will be used this year for Intel AlderLake and DG2.It is only for the GPU link but I would see a general use if GPU, CPU and SSD are all supporting it. Guess that would be enough for most consumers.

I am not sure if ResizableBAR and DirectStorage profit from PCIe 5.0/6.0 a lot but if it would obviously be nice to have at least GPU, CPU and SSD connected with newer PCIe and maybe even iclude RAM addressing over CXL / CCIX.

You do not need the whole chipset supporting it - just the direct lines from the CPU to GPU, CPU, SSD and I/0 while the others stay on PCIe 4.0

mode_13h - Wednesday, May 26, 2021 - link

> first PCIe 5.0 will be used this year for Intel AlderLake and DG2. It is only for the GPU linkHow do you know this?

> You do not need the whole chipset supporting it

The board needs to support it, which means more layers and retimers. That adds cost.

And remember how AMD X570 boards started showing up with cooling fans on the chipsets? If PCIe 4.0 used that much more power, just imagine *another* doubling of clock speed! Yeah, maybe not in the southbridge, but no matter where you put it, get ready to burn some real power on I/O.

mode_13h - Wednesday, May 26, 2021 - link

> That adds cost.Also, more exotic PCB materials. And repeat for each device that supports it.

Matthias B V - Wednesday, June 9, 2021 - link

This is based on current information about AlderLake and DG2 which seems to indicate that AlderLake has a 16x PCIe 5.0 link and DG2 has a PCIe 5.0 link.Yes the board needs to support it but you can limit it to one GPU link and one SSD link that are close to the CPU. The other lanes and chipset can be kept simple.

Yes X570 was hot but that is mainly because they used an Ryzen I/O instead of a specific chipset like the B550.

Yojimbo - Wednesday, May 26, 2021 - link

Yes, but how does that not make what I said less relevant? What you are saying is that the time stamp given to PCIe 1.0 is not at the same standard of the time stamp as PCIe 5.0 or PCIe 6.0, and the difference is in such a direction to give the impression that PCIe 6.0 is coming sooner after PCIe 1.0 than it really is. So if we had uniformity of time stamps then PCIe 6.0 would be behind a "doubling every three years" cadence from PCIe 1.0.mode_13h - Wednesday, May 26, 2021 - link

> more importantly how inadequate PCI, AGP and VESA were.Woah, that's a huge blurring-together of technologies spanning a whole decade!

IIRC, AGP 8x wasn't too slow, though a x16 PCIe 1.0 slot was almost 2x as fast. The bigger benefit of PCIe was for the non-graphics slots, which were generally stuck on 32-bit PCI @ 33 MHz.

p1esk - Wednesday, May 26, 2021 - link

So looks like we are going to go straight from PCIe 4.0 to PCIe 6.0 in a couple of years. Why did they even bother talking about PCIe 5.0?