Intel to Revive ‘Tick-Tock’ Model, Unquestioned CPU Leadership Performance in 2024/2025

by Dr. Ian Cutress on March 23, 2021 6:31 PM EST- Posted in

- CPUs

- Intel

- Tick-Tock

- 7nm

- Chiplets

- Pat Gelsinger

- Meteor Lake

- Tiles

As part of today’s announcements, during Intel’s Q&A session after the prepared remarks, CEO Pat Gelsinger explained how Intel is going to revive its fortunes when it comes to its leading edge compute products. One of Gelsinger’s mantras seems to be that unquestioned leadership products bring unquestioned leadership margins for those products, and for Intel to execute, it needs to return to its days of old.

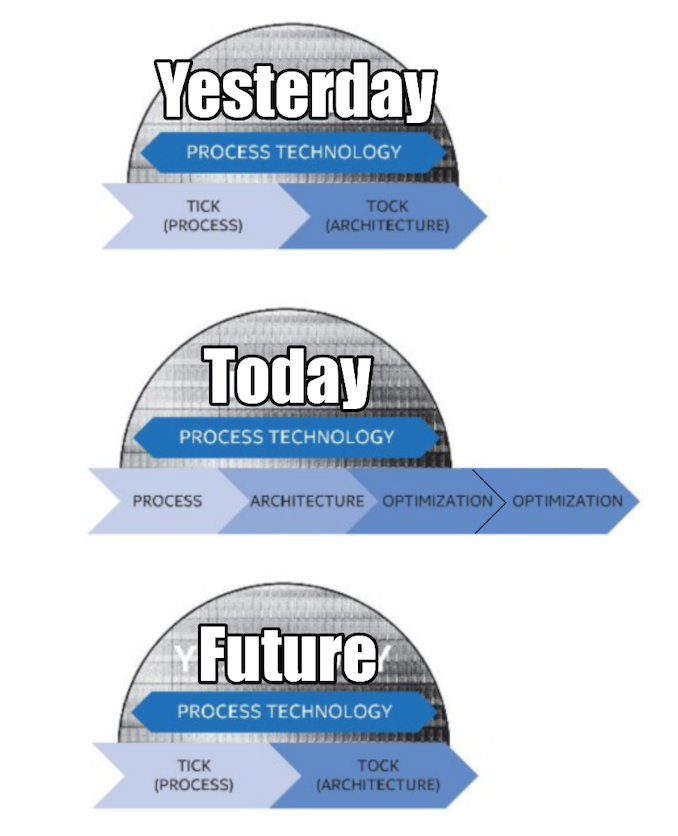

In the past, through the 1990s, 2000s, and into the 2010s, Intel’s manufacturing philosophy was known as ‘Tick-Tock’. This means that for every product generation, the leading edge compute hardware was either a Tick (process node enhancement), or a Tock (microarchitecture enhancement). Each generation would alternate between the two, allowing Intel to take advantage of a familiar design on a new process node, or using a mature node to enable a new performance-focused design. That policy was scuppered when delays to Intel’s 10nm forced Intel into more of a Tick-Tock-Optimization-Optimization-Optimization model.

Today CEO Pat Gelsinger stated that at Intel’s core it has to re-establish the Tick-Tock model that enabled repeated leadership in the CPU ecosystem, buoyed by a healthy CPU roadmap. Part of this is re-establishing discipline in Intel’s ranks to continually provide both microarchitecture updates and process node updates on a regular expected cadence. Pat stated as part of the call that Intel will look towards a confirmed yearly process node improvement, and as a result, there might be a lot of Ticks in the future, with a push to more Tocks as well.

On top of this commentary, Pat Gelsinger also stated that Intel’s CPU roadmaps are already baked in through 2021, 2022, and 2023. The company is thus looking to 2024/2025 for ‘unquestioned CPU leadership performance’, which traditionally means the fastest processor for single thread and multi-thread workloads. This is for sure a laudable goal, however Intel will also have to adapt to a changing landscape of chiplet processor designs (coming in 2023), enhancing on-die accelerators (GNA already present), and also what it means to have leadership performance – in the modern era, leadership performance doesn’t mean much if you’re also pushing lots of Watts. Intel stated that its 7nm process is now comfortably on track to deliver Meteor Lake, a client CPU using tiles/chiplets, in 2023, however we are likely looking to a 7nm variant or even external processes for a 2024/2025 product. Intel has also stated that it is looking to consider the core of its leading edge compute on external foundry processes, although one might argue that this doesn’t explicitly say ‘CPU’.

It is also worth noting that Intel/Gelsinger isn’t calling its disaggregated silicon as ‘chiplets’, and prefers to use the term ‘tiles’. This is because Intel’s tiles amount to long wires across 3D packaging technologies like EMIB and Foveros, compared to package-based multi-die interconnect that require buffers as well as control fabric. Tiles by this definition are more costly to implement than chiplets, and have additional thermal considerations by having high-powered silicon close together, so it will be interesting to see how Intel balances these new packaging technologies with the more cost-sensitive elements of its portfolio, such as client processors.

It’s been known that Intel’s microarchitecture teams haven’t been idle waiting for 10nm to come through the pipe, with a number of designs ready and waiting to go for when the process node technology matures. With any luck, if Intel can get a headwind with 7nm, when 2024 rolls around it might all come thick and fast.

109 Comments

View All Comments

drothgery - Wednesday, March 24, 2021 - link

If Intel only had their early 14nm-level problems with 10nm and 7nm, they'd have 7nm mobile chips out *now*.Spunjji - Friday, March 26, 2021 - link

14nm was the early warning signs that all was not well in paradise - it arrived later than expected and the initial results were underwhelming.Sometimes I wonder how good 22nm would have looked if they'd kept improving it like they eventually did with 14nm, rather than trying to kick it out the door ASAP.

SaturnusDK - Wednesday, March 24, 2021 - link

" Intel stated that its 7nm process is now comfortably on track to deliver Meteor Lake, a client CPU using tiles/chiplets, in 2023...."Let me check the TSMC process node roadmap as reported here on Anandtech real quick..

TSMC expects to enter full volume production on 3nm in 22H2.

Auch Intel. Even if we assume the Intel 7nm is comparable to one form of TSMC 5nm that still means they're at least a full process node behind in 2023.

mattbe - Wednesday, March 24, 2021 - link

"TSMC expects to enter full volume production on 3nm in 22H2."With only enough supply for Apple and possibly Huawei. There won't be capacity available from AMD until at least 2023.

You are right they are still a node behind even if 7nm comes out in 2023. There's a lot of catching up for Intel to do if they want to take back the processing lead.

Bagheera - Friday, March 26, 2021 - link

Huawei for kicked off TSMC client list last year. AMD is on track to become TSMC's second largest customer.Danvelopment - Wednesday, March 24, 2021 - link

The "Today" on that image is missing about 15 "Optimisation" items.Rudde - Wednesday, March 24, 2021 - link

Kaby Lake, Coffee Lake, Coffee Lake R, Comet Lake. Rocket lake is tock. Tick tock opt opt opt opt tock.duploxxx - Wednesday, March 24, 2021 - link

Well the show is there, that was needed off course from CEO perspective, the show must go on.Now the facts, the bleeding is hurting a lot....and will continue for a very long time.

Bad 10nm process, bad core re-designs, bad roadmap. Desktop is waiting for Alderlake which is again not scale the Core count, Ice lake is hardly improving anything (few cores more and finally more memory lanes) and Eagle is another year out.

So its 2023-2024 to get back on track with no idea where the competition will be at that point.

Lost apple as a customer by that time in all the segments, lost at least 30% marketshare by that time to AMD. Have no footage in mobile phone devices, GPU has yet to be seen if it will any change of taking off....

Adding 2 fabs? they will have spare capacity by the time they are ready... but they will always sell lots of stuff even if it is bad since the OEM market is so broken ECO system and R&D sponsoring.

edzieba - Wednesday, March 24, 2021 - link

"Tiles by this definition are more costly to implement than chiplets, and have additional thermal considerations by having high-powered silicon close together"Through-substrate interconnects have their own thermal issues: both ends of every link require drivers, which are pure power waste. The more links (i.e. the more chiplets you split the design into) the more power is spent for no useful output: https://www.anandtech.com/show/13124/the-amd-threa... . Inter-die (EMIB, Foveros, etc) routing has minimal overhead over routing over the same area monolithic die.

While stacked dies complicate internal thermal management (Z- conduction path), they also mean total package thermal management is simpler (reduced total thermal power, smaller physical package).

JayNor - Wednesday, March 24, 2021 - link

What would you call the more than 40 pieces in the xe-hpc?Most of it is foveros stacked chiplets. Perhaps he refers to the emib connected units as tiles.