PCIe 6.0 Dev Reaches v0.3; On-Track for a Full Specification In 2021

by Ryan Smith on October 15, 2019 10:30 AM EST

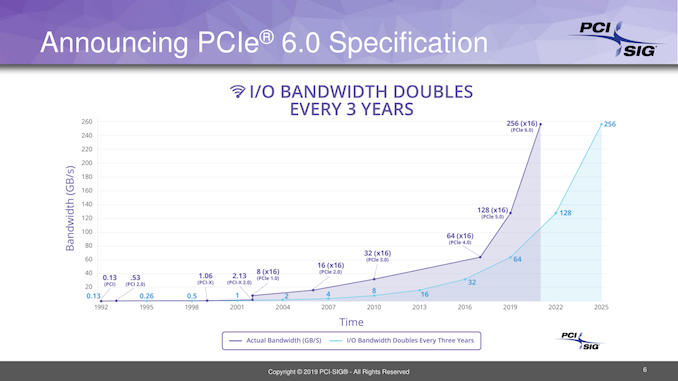

Having wrapped up their work on the PCI-Express 5.0 specification earlier this year, the PCI-SIG wasted no time in getting to work on the next version of the specification, PCIe 6.0. That specification, which is expected to be finished in 2021, will once again double PCIe’s bandwidth to 64 GigaTransfers/second – or roughly 128GB/sec (each direction) for a x16 slot – thanks to some high-end encoding technologies like PAM4.

At the time that PCIe 6.0 was first announced, the group was just beginning work on the specification. And now a few scant months later, the group has released a brief update, announcing that they have already completed version 0.3 of the new spec.

The announcement itself is light on technical details, as the design goals and major underlying technologies for PCIe 6.0 were announced at the very start of the project. However the organization is keen to ensure that PCIe development continues moving at a steady pace, to avoid repeating the long gap between 3.0 and 4.0.

And the group’s members will certainly be busy. Even with the 0.3 specification in hand, it’s going to be nearly another two years before the specification is done, reflecting on the fact that there’s a lot of work left to be done to solve the technical challenges in developing PCIe 6.0, and bringing new signaling standards into the specification while maintaining backwards compatibility.

Source: PCI-SIG

45 Comments

View All Comments

DanNeely - Tuesday, October 15, 2019 - link

Both. Flash storage server builders want to only use a single PCIe lane per drive so they can cram more in. That means they need faster interconnects a lot more than consumer drives to. PCIe5 x1 finally lets them get the performance of a PCIe3 x4 drive in a single lane. PCIe6 will give parity with the PCEe4 x4 drives that will be coming out in the next year or two.x8/16 slots with higher bandwidth are needed for accelerator cards; both of the super high end version of normal GPU variety (which can bottleneck if running something chatty with the CPU or that needs to stream data from system ram/SSDs because it can't fit into the GPUs ram, and the custom AI accelerators that all the big tech companies are making. 40/100gigabit networking standards also will benefit from needing fewer lanes/adapter to implement.

thomasg - Tuesday, October 15, 2019 - link

There are plenty of reasons.PCIe is not being driven by the demand of home-PCs, it's widely used for all kinds of interfaces in professional usecases.

For example, InfiniBand right now supports 250 Gbit/s links.

For a single link, it can't be done with PCIe 3.0 x16.

PCIe 4.0 x16 barely manages, but then a single link uses up the full 16 lanes.

PCIe 5.0 allows a InfiniBand link in just 8 lanes, so machines will be able to support 2 links as soon as PCIe 5.0 is available.

400 Gigabit Ethernet will be available soon, and again, requires a full x16 link for a single port with PCIe 5.0.

PCIe 6.0 will allow 2 links.

Storage also manages to utilize more than enough PCIe lanes.

When PCIe 6.0 will be available 4-5 years from now, there will be plenty of usecases.

rahvin - Tuesday, October 15, 2019 - link

Try 6 years at the earliest. From standard _completion_ till the first deliveries of hardware it's usually 3 years. And that's if manufacturers start right away on support. Intel avoided PCIe4 in favor a waiting a couple more years for 5.0 so will probably be a year late when they scab it onto some new 14++++mm processor down the road. If AMD hadn't moved forward we might have even skipped 4.0 entirely. But the key point here is it takes 3 years for the chip manufactures to receive the completed spec, build it into their designs and chipsets and then fab silicon, and that will only happen if they jump right on it.PCIe4 was competed roughly 3 years ago. PCIe5 was just completed so we should see the first hardware in 2022-2023 (depending on chip fabrication schedules). PCIe6 isn't even a completed standard, and isn't likely to be finished for at least a few years. In particular with 6.0 there as some serious political issues (between participants) that could hold it up even longer, at least from what I've read.

At least PCIe moves faster than USB does, USB takes 10 f'n years to reach broad deployment for each version.

thomasg - Monday, October 21, 2019 - link

PCI-SIG has stepped up its game. PCIe 4.0 was a long time in the making, but they moved swiftly to PCIe 5.0 which will be available shortly.PCIe 6.0 is coming along nicely and I expect the first 0.5 draft by 2021, as planned.

There's no magic required for PCIe 6.0: they have a solid plan based on widely used technologies and their main job is working out the details (which isn't easy, but also not overly ambitious).

If the final draft will take longer, there might be early adopters, basing hardware on the 0.7 draft, as IBM did with POWER9 due to the delays with PCIe 4.0.

CaedenV - Wednesday, October 16, 2019 - link

400gbps...i would love to see anything faster than 1gbps come standard these days!thomasg - Monday, October 21, 2019 - link

In my field, 10 Gbit/s is absolutely standard (every device I work with has at least 15 ports supporting 10,3 Gbit/s), and we're in the process of moving to 40 Gbit/s for Ethernet and 25 Gbit/s for everything else.The consumer market is more and more getting irrelevant and moving more and more slowly.

Very few users actually care about wire networks at all; all that's relevant is fast WiFi and fast cellular, and a couple of years from now, the usage of wire-based Ethernet will certainly be in the single-digit percentage.

When landlines move to fibre over 1 Gbit/s - which is still very rare - the vast majority of users will only connect their all-in-one router to the fibre directly and use no 10 GbE at all.

bcronce - Tuesday, October 15, 2019 - link

PCIe 5.0 is less about higher bandwidth and more about reduced traces. Fewer traces are more compact and easier to design. I assume 6.0 is a similar thing. Why have a 4x slot of PCIe 3.0 when you can have a 1x of 5.0? Imagine video cards with 2x PCIe 6.0.The bandwidth increase also makes it useful for certain situations that used to require special protocols, like "fabrics". We're also fast approaching non-volatile memory. A use case around that is a unified memory/storage system. Instead of 32GiB of memory and a 1TiB SSD, you instead just have 1TiB of non-volatile memory. Having ridiculously high speed connections will become more important.

Santoval - Tuesday, October 15, 2019 - link

40 to 60 MB/s speeds have long been possible with mechanical hard disks (albeit at a pitiful IOPS rate) so no, that is certainly not the "typical performance" of SSDs. Unless you meant low-mid range SD cards. SATA3 can also provide up to ~500 MB/s, so you got that wrong as well.Fewer but faster lanes is one of the reasons faster PCIe revisions are developed, but not the only reason. PCIe 5.0 and above is highly desirable as the PHY layer of interconnect protocols for CPU chiplets (e.g. a future revision of Infinity Fabric), for GPU chiplets, for Infiniband networking for datacenters, for faster Ethernet, for SSDs (naturally), for silicon photonics, for next gen protocols like Gen-Z or CXL, for a future version of USB, Thunderbolt, DisplayPort etc etc

The list goes on and on, but the major application is for servers and datacenters. If the industry switches en masse to CPU and GPU chiplets that would be the consumer application that could gain most from faster PCIe revisions (unlike SSDs which need faster NAND or a faster controller with more channels to take advantage of the higher PCIe bandwidth, and unlike graphics cards which gain little from the switch to a new PCIe revision).

danielfranklin - Wednesday, October 16, 2019 - link

And lucky for us you aren't running the internet's largest websites, data-storage or AI clusters on it.You could run a Pentium 4 without any real issue for those tasks....

Urufu - Friday, October 18, 2019 - link

I just find this statement silly , I mean a dude might ask himself why researchers are working like demons for a more comfortable maxi pad when he himself has no need of such and refuses to acknowledge a portion of the population does indeed need something like this. Basically , it's a troll question even if the askee doesn't realize it.