Intel’s LGA4189-4 and LGA4189-5 for Cooper Lake & Ice Lake CPUs Now Available

by Anton Shilov on September 2, 2019 10:35 AM EST- Posted in

- CPUs

- Intel

- Ice Lake

- Xeon Scalable

- LGA4189

- Cooper Lake

TE Connectivity, a maker of various connectivity solutions, has introduced its newly-developed LGA4189 sockets for Intel’s next-generation Xeon Scalable processors supporting PCIe Gen 4. The products have been validated by Intel and are therefore ready for production of motherboards aimed at next-gen servers. It is worth noting that we already know some Cooper Lake systems are already deployed at large companies, suggesting that some LGA4189 sockets have been validated already.

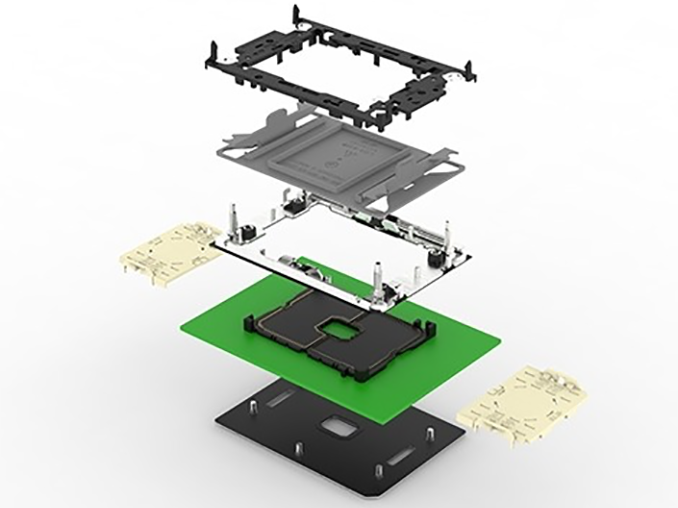

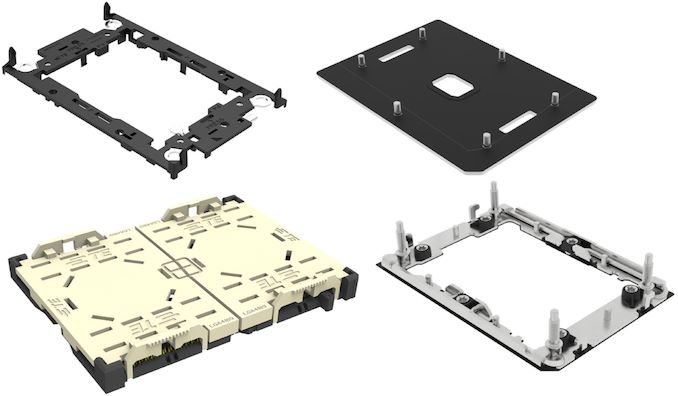

TE offers LGA4189-4 and LGA3189-5 sockets (which are called Socket P4 and Socket P5), appropriate backplates, compatible bolster plates, mounting mechanisms, and dust covers. As discovered previously, Intel’s next-generation Xeon Scalable processors in LGA4189 packaging will feature a native eight-channel memory controller and PCIe 4.0, with at least eight channel memory on standard configurations.

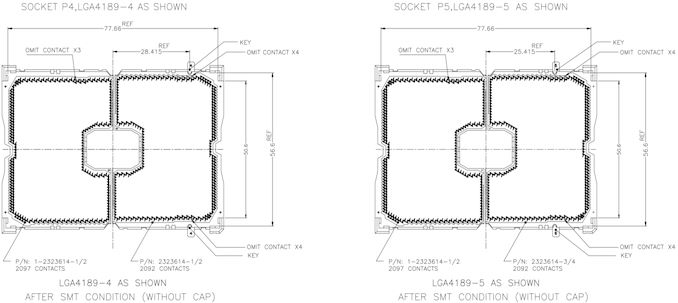

One interesting thing to note is that TE Connectivity will offer Intel’s LGA 4189 socket in two versions: the LGA4189-4 (branded as Socket P4) and the LGA4189-5 (branded as Socket P5). Being a socket maker, TE indicates that key features of Socket P4 and Socket P5 are the same: they have the same pin count, the same 0.9906 mm hex pitch, the same SP height of 2.7 mm, and the same mounting mechanisms. Meanwhile, the company does not disclose why Intel needed two separate 4189-pin sockets. Keeping in mind that Intel will have two next-generation Xeon Scalable processors — codenamed Cooper Lake and Ice Lake — it looks like that the the single-die CPUs and multi-die CPUs will use different sockets and will not be pin-to-pin compatible despite the fact that they are going to use the same platform.

A 4189-pin socket that has to provide sufficient 56-core power and support ultra-fast interconnections is extremely complex to build. TE is currently “one of the few manufacturers that can provide sockets and hardware” for Intel’s next-gen server CPUs, the company said. Meanwhile, TE says that its LGA4189 hardware is now available to interested parties, such as server makers.

Related Reading

- Power Stamp Alliance Exposes Ice Lake Xeon Details: LGA4189 and 8-Channel Memory

- Intel Xeon Update: Ice Lake and Cooper Lake Sampling, Faster Future Updates

- Intel to Offer Socketed 56-core Cooper Lake Xeon Scalable in new Socket Compatible with Ice Lake

- Intel Architecture Manual Updates: bfloat16 for Cooper Lake Xeon Scalable Only?

- Cisco Documents Shed Light on Cascade Lake, Cooper Lake, and Ice Lake for Servers

Source: TE Connectivity

31 Comments

View All Comments

Kevin G - Tuesday, September 3, 2019 - link

Intel and IBM has explored replacing some of the copper links with optical which mechanically would be safer since the methods they use don't have any point that could bend. However, these companies have only shown off prototypes and there is a such a crisscross of patents that without any sort of mutual licensing agreement, keeps this technology in their labs.mode_13h - Monday, September 2, 2019 - link

It's a natural consequence of more cores per CPU. The benefit is that you need fewer discrete CPUs to achieve a given core count and that means fewer sockets and motherboard traces between them. So, if you need a certain number of cores, increased integration actually provides a cost savings.A good question whether server CPUs will top out at 8-channel memory and 130-lane PCIe, or just keep on going. A lot of that probably has to do with efficiency-scaling beyond 64 cores. At some point, the interconnect power & maintaining cache coherency starts to dominate power dissipation.

PixyMisa - Monday, September 2, 2019 - link

IBM is using 25Gbps memory interfaces on their new Power 9 chips, so they need far fewer pins for the same memory bandwidth.So we're probably stuck with pins, but we could reduce the number significantly if we run the signals faster.

willis936 - Monday, September 2, 2019 - link

TNSTAAFLCranking bitrate burns up power and transistor budget. Keeping it low means more pins (at significant cost). Which solution is better is mostly dictated by the economics at the time and what workload the system is tuned for.

stephenbrooks - Monday, September 2, 2019 - link

0.9906 mm hex pitch = 39 mils exactlySantoval - Monday, September 2, 2019 - link

"As discovered previously, Intel’s next-generation Xeon Scalable processors in LGA4189 packaging will feature a native eight-channel memory controller and PCIe 4.0, with at least eight channel memory on standard configurations."You link only has information about Ice Lake Xeon CPUs, not Cooper Lake ones. That paragraph -and your entire article basically- makes it sound like Cooper Lake Xeons will also support PCIe 4.0 (and 8-channel memory?) but I doubt that's the case.

It rather looks like that Cooper Lake Xeons will be used on a new platform that fully supports PCIe 4.0 but the CPUs themselves will only have a PCIe 3.0 controller. So while moving to Ice Lake Xeons (and taking advantage of PCIe 4.0) later on would be an easy switch, since they share the same platform, Cooper Lake Xeons will only work in PCIe 3.0 mode. Which makes the point of Cooper Lake even more questionable, unless Ice Lake Xeons are going to be released in 2H 2020.

Kevin G - Tuesday, September 3, 2019 - link

Cooper Lake has a handful of instructions not found on Ice Lake that will be useful for the AI/machine learning crowd.It also doesn't hurt Intel to have a plan B available if they run into 10 nm supply issues.

dairyAT - Monday, September 2, 2019 - link

IN B4 software companies start licencing price per pin.Xyler94 - Wednesday, September 4, 2019 - link

Don't give them ideas!MDD1963 - Tuesday, September 3, 2019 - link

2nd paragraph references both LGA4189-4 and LGA3189-5....is that accurate, or a typo?