HiSilicon Kirin 970 - Android SoC Power & Performance Overview

by Andrei Frumusanu on January 22, 2018 9:15 AM EST

Today I would say that there’s only two truly vertically integrated mobile OEMs who have full control over their silicon: Apple and Huawei – and of the two one could say Huawei is currently even more integrated due to in-house modem development. Huawei’s semiconductor division, HiSilicon, has over the last several years been the one company which seems to have managed what the others haven’t: break in into the high-end market with solutions that are competitive with the current leader in the business, Qualcomm.

I remember the Honor 6 with the newly branded (Previously not having any “halo” line-up name) Kirin 920 SoC as the first device with the company’s in-house SoC that we reviewed. These and the following generation the Kirin 930 suffered from immaturity with problems such as a very power hungry memory controller and very disappointing camera processing pipeline (ISP/DSP). The Kirin 950 was in my opinion a turning point for HiSilicon as the product truly impressed and improved the quality of the product, catching many eyes in the semiconductor industry, including myself in the resulting review of the Huawei Mate 8.

Over the last several years we’ve seen great amounts of consolidation in the mobile semiconductor industry. Companies such as Texas Instruments which were once key players no longer offer mobile SoC products in their catalogue. We’ve seen companies such as Nvidia try and repeatedly fail at carving out meaningful market-share. MediaTek has tried providing higher end SoCs with the Helio X line-up with rather little success to the point that the company has put on hold development in that segment to rather focus on higher margin parts in the P-series.

Meanwhile even Samsung LSI, while having a relatively good product with its flagship Exynos series, still has not managed to win over the trust of the conglomorate's own mobile division. Rather than using Exynos as an exclusive keystone component of the Galaxy series, Samsing has instead been dual-sourcing it along with Qualcomm’s Snapdragon SoCs. It’s therefore not hard to make the claim that producing competitive high-end SoCs and semiconductor components is a really hard business.

Last year’s Kirin 960 was a bit of a mixed bag: the SoC still delivered good improvements over the Kirin 950 however it was limited in terms of what it could achieve against competing flagship SoCs from Samsung and Qualcomm as they both had a process node advantage. Huawei's introduction of flagships with new generation of SoCs in the fourth quarter is more close to the release time-frame of Apple than the usual first quarter that we’ve come accustomed of Qualcomm and Samsung.

As such when pitting the Kirin versus Snapdragon and Exynos’s we’re looking at a product that’s more often than not late to the party in terms of introduction of new technologies such as process node and IP. The Kirin 970 fits this profile: as a 10nm Cortex-A73 generation-based SoC, it lagged behind Qualcomm and Samsung in terms of process node, yet being too early in its release to match up with ARM’s release schedule to be able to adopt DynamiQ and A75 and A55 based CPU cores for this cycle. That being said the Kirin 970 enjoys a few months with technical feature parity with the Snapdragon 835 and Exynos 8895 before we see new Snapdragon 845 and Exynos 9810 products later in the usual spring refresh cycle.

Nevertheless, the article today is a focus on the Kirin 970 and its improvements and also an opportunity to review the current state of SoCs powering Android devices.

| HiSilicon High-End Kirin SoC Lineup | |||

| SoC | Kirin 970 | Kirin 960 | Kirin 950/955 |

| CPU | 4x A73 @ 2.36 GHz 4x A53 @ 1.84 GHz |

4x A73 @ 2.36GHz 4x A53 @ 1.84GHz |

4x A72 @ 2.30/2.52GHz 4x A53 @ 1.81GHz |

| GPU | ARM Mali-G72MP12 746 MHz |

ARM Mali-G71MP8 1037MHz |

ARM Mali-T880MP4 900MHz |

| LPDDR4 Memory |

4x 16-bit CH LPDDR4 @ 1833 MHz 29.9GB/s |

4x 16-bit CH LPDDR4 @ 1866MHz 29.9GB/s |

2x 32-bit LPDDR4 @ 1333MHz 21.3GB/s |

| Interconnect | ARM CCI | ARM CCI-550 | ARM CCI-400 |

| Storage I/F | UFS 2.1 | UFS 2.1 | eMMC 5.0 |

| ISP/Camera | Dual 14-bit ISP | Dual 14-bit ISP (Improved) |

Dual 14-bit ISP 940MP/s |

| Encode/Decode | 2160p60 Decode 2160p30 Encode |

2160p30 HEVC & H.264 Decode & Encode 2160p60 HEVC Decode |

1080p H.264 Decode & Encode 2160p30 HEVC Decode |

| Integrated Modem | Kirin 970 Integrated LTE (Category 18/13) DL = 1200 Mbps 5x20MHz CA, 256-QAM UL = 150 Mbps 2x20MHz CA, 64-QAM |

Kirin 960 Integrated LTE (Category 12/13) DL = 600Mbps 4x20MHz CA, 64-QAM UL = 150Mbps 2x20MHz CA, 64-QAM |

Balong Integrated LTE (Category 6) DL = 300Mbps 2x20MHz CA, 64-QAM UL = 50Mbps 1x20MHz CA, 16-QAM |

| Sensor Hub | i7 | i6 | i5 |

| NPU | Yes | No | No |

| Mfc. Process | TSMC 10nm | TSMC 16nm FFC | TSMC 16nm FF+ |

The Kirin 970, isn't a major IP overhaul as it continues to use the same central processing unit IP from ARM that was used in the Kirin 960. The new SoC even doesn't improve the frequency of the CPU clusters as we still see the same 2.36GHz for the A73 cores and 1.84GHz for the A53 cores. When ARM originally launched the A73 we had seen optimistic targets of up to 2.8GHz on TSMC 10nm, but we seem to have largely missed that target, a sign of ever increasing difficulty to scale frequency in mobile SoCs as the diminishing returns from process node updates become worse and worse.

The Kirin 970 does bring a major overhaul and change in the GPU configuration as we see the first implementation of ARM’s Mali G72 in a 12-cluster configuration, a 50% increase in core count over the Kirin 960’s G71-MP8 setup. The new GPU is running at a much reduced frequency of 746MHz versus the 1033MHz of the Kirin 960. In Matt Humrick’s review of the Kirin 960 we saw some disastrous peak average power figures of the Mali G71 outright exploding the thermal envelope of the Mate 9, so hopefully the architectural improvements of the new G72 alongside a wider and lower clocked configuration in conjunction with the new process node will bring significant improvements over its predecessor.

The new modem in the Kirin 970 now implements 3GPP LTE Release 13 and supports downlink speeds of up to 1200Mbps thanks to up to 5x20MHz carrier aggregation with 256-QAM, making the new Kirin modem feature equivalent to Qualcomm’s X20 modem that’ll be integrated in the Snapdragon 845.

The big story surrounding the Kirin 970 was the inclusion of a dedicated neural processing unit. The NPU, as HiSilicon decided to name it, is part of a new type and generation of specialised dedicated acceleration blocks with the aim of offloading “inferencing” of convolutional neural net (CNNs). Many will have heard buzzwords such as artificial intelligence surrounding the topic, but the correct term is machine learning or deep learning. The hardware acceleration blocks with various names from various companies do not actually do any deep learning, but rather are there to improve execution (inferencing) of neural network models while the training of the models will still remain something that will be done either in the cloud or by other blocks in the SoC such as the GPU. It’s still the early days but we’ll have a proper look at the NPU in its dedicated section of the article.

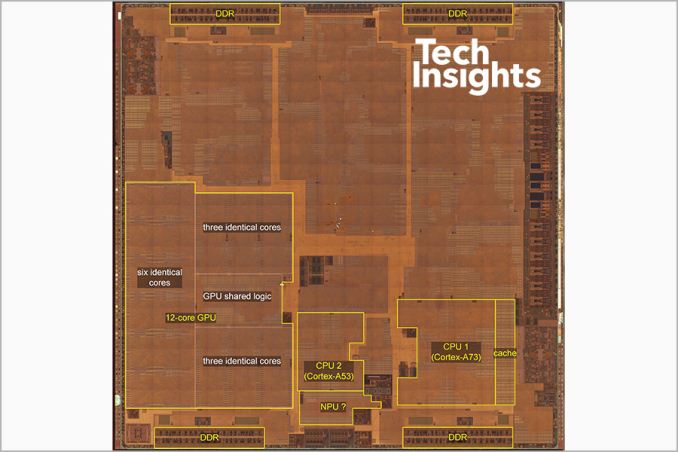

SoC die shot image & labels courtesy of TechInsights Mate 10 teardown

As aforementioned one of the bigger improvements of the Kirin 970 is the switch to a TSMC 10FF manufacturing node. While 10nm is supposed to be a long-lived node for Samsung's foundry – where indeed we’ll see two full generations of SoCs produced on 10LPE and 10LPP – TSMC is taking a different approach and sees its own 10FF process node a short-lived node and stepping-stone to the much anticipated 7FF node, which is to be introduced later in 2018. As such the only TSMC 10FF mobile products to date have been the low-volume MediaTek X30 and Apple 10X in summer and the high-volume Apple A11 and HiSilicon Kirin 970 in Q3-Q4, a 2-3 quarter after Samsung had entered high-volume production of the Snapdragon 835 and Exynos 8895.

HiSilicon’s expectations of the new process node are rather conservative improvement of only 20% in efficiency at the same performance point for the apples-to-apples CPU clusters, below ARM’s earlier predictions of 30%. This rather meagre improvement in power will be likely one of the reasons why HiSilicon decided not to increase the CPU clocks on the Kirin 970, instead focusing on bringing down power usage and lowering the TDP when compared to the Kirin 960.

The SoC does enjoy a healthy die size shrink from 117.72mm² down to 96.72mm² even though the new SoC has 50% more GPU cores as well as new IP blocks such as the NPU. Our colleagues at TechInsights have published a detailed per-block size comparison between the Kirin 960 and Kirin 970 and we see a 30-38% decrease in block size for apples-to-apples IP. The Cortex-A73 quad-core cluster now comes in at only 5.66mm², a metric to keep in mind and in stark contrast to Apple which is investing twice as much silicon area in its dual-core big CPU cluster.

116 Comments

View All Comments

Hairses - Monday, January 22, 2018 - link

I think I see what you mean, but the graphs themselves need work. It's not clear which axis belongs to which data point, and the scaling/notation on the left axis makes no sense. If you look at some of them, quite often the longest data bar has a mark showing a value somewhere halfway between two data points with bars smaller than it. So it less to confusion; is the length of the bar one metric, and the mark another? And it's not that the bars are reversed scale either. It's not even clear why there are two axis at all, now I take a second look.It's a good idea for a viz, but needs some rejigging. Maybe it looks clearer on desktop, mobile may be too small.

GreenReaper - Thursday, January 25, 2018 - link

I agree with Hairses; that the graph - and in particular its legend - could do with revision.At first I thought the CPU was faster than the NPU because the arrows seemed to be pointing at the end which related to the measurement in question - instead it seems the intent was "travelling in this direction". You could perhaps keep the text and arrows the same, but position them at the relevant sides of the graph.

gregounech - Monday, January 22, 2018 - link

This is the reason why I read Anandtech, good job Andrei.hlovatt - Monday, January 22, 2018 - link

Great article. Any chance of same for Apple?Andrei Frumusanu - Monday, January 22, 2018 - link

As mentioned in the article, Apple stuff is a lot harder. Measuring power efficiency for example requires me to tear down an iPhone to tap the battery. It's my goal for the future as I work through the backlog of articles.lilmoe - Monday, January 22, 2018 - link

If you're going the extra mile, it would be nice to see multiple generations of Apple SoCs tested, not just the A11. Thanks.mczak - Monday, January 22, 2018 - link

Great article.I'd have liked to see though GPU efficiency figures at sustained power levels. Not that it should reverse the outcome, but I would expect the efficiency of the newest Samsung/Qualcomm/Hisilicon chips to be a bit closer then.

Andrei Frumusanu - Monday, January 22, 2018 - link

It's something that I'm considering doing for device reviews (Sustained power levels obviously differ between devices).jospoortvliet - Saturday, January 27, 2018 - link

Another issue might be the silicon lottery... hard to deal with but especially small differences might be due to a particularly leaky or good piece of silicon...Wardrive86 - Monday, January 22, 2018 - link

Excellent article! Hope to see many more like this. I wish the mid range could also be included but I understand how time consuming these tests were. Great job, well done!