The Intel Skylake-X Review: Core i9 7900X, i7 7820X and i7 7800X Tested

by Ian Cutress on June 19, 2017 9:01 AM ESTThe Basin Falls Platform: X299, SKL-X, & KBL-X

For most practical definitions of the Basin Falls platform, the X299 chipset is the heart. X299 supports the new processors, and like the Z170 and Z270 counterparts on the mainstream consumer line, is basically a big PCIe switch. One of the issues with the older X99 chipset was its limited capabilities, and inability to drive many PCIe devices – this changes with the big switch mentality on X299. For the DMI 3.0 link going into the chipset (basically a PCIe 3.0 x4), the chipset has access to up to 24 PCIe 3.0 lanes for network controllers, RAID controllers, USB 3.1 controllers, Thunderbolt controllers, SATA controllers, 10GbE controllers, audio cards, more PCIe slot support, special controllers, accelerators, and anything else that requires PCIe lanes in either an x4, x2 or x1 link. The total uplink is limited by the DMI 3.0 link, but there will be very few situations where this is saturated. There are a few limits to what support is available (some ports are restricted in what they can handle), and only three PCIe 3.0 x4 drives can use the in-built PCIe RAID, but this should satiate all but the most hardcore enthusiasts.

The Skylake-X family of processors for Basin Falls comes in two stages, based on the way the processors are developed. Normally HEDT processors are cut down versions of enterprise processors, usually through restricting certain functions, but the enterprise processors are typically derived from three different silicon layouts during manufacturing. Internally Intel call these three layouts the LCC (low core-count), HCC (high core-count) and XCC (extreme core-count), based on the maximum number of cores they support. Nominally Intel does not disclose which silicon layout they use for which processors, though it is usually straight forward to work them out as long as Intel has disclosed what the configurations of the LCC/HCC/XCC dies are. In this case, Intel has officially left everyone guessing, but the point here is that historically Intel only uses the LCC silicon from the enterprise line for its consumer desktop processors.

In previous generations, this meant either a 6, 8 or 10 core processor at the top of the stack for consumers, with lower core count models being provided by binning/salvaging imperfect CPUs. Each year we expected one of two things: the top-end SKU either gets more frequency, less power, or more cores, and as such the march of progress has been predictable. If you had asked us two months ago, we would have fully expected Skylake-X to top out with LCC silicon at 10 or 12 cores, depending on how Intel was planning the manufacturing part.

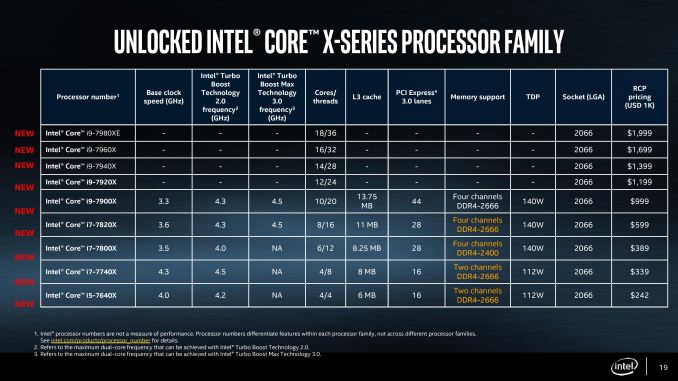

So the first element of Intel’s launch is the LCC processors, running up to 10 cores. We previously published that the LCC silicon was 12 cores, but we can now show it is 10 – more on that later. The three Skylake-X CPUs launching today are using LCC silicon with 6, 8 or 10 cores as the Core i7-7800X, Core i7-7820X and Core i9-7900X respectively. Intel is further separating these parts by adjusting the level of official supported DRAM frequency, as well as the PCIe lanes. We’ll go in a bit more detail further in the review.

The second element to the Skylake-X launch is the one that has somewhat surprised most of the industry: the launch will contain four processors based on the HCC silicon. Technically these processors will not be out until Q4 this year (one SKU coming out in August), and the fact that Intel did not have frequency numbers to share when announcing these parts shows that they are not finalized, calling into question when they were added to the roadmap (and if they were a direct response to AMD announcing a 16-core part for this summer). We’ve written a detailed analysis on this in our launch coverage, and we’ll cover some of the topics in this review. But Intel is set to launch 12, 14, 16 and 18-core consumer level processors later this year, with the top part running a tray price (when you buy 1k CPUs at a time) of $1999, so we expect the retail to be nearer $2099.

It should be noted that due to a number of factors, the Skylake-X cores and the communication pathways therein are built slightly differently to the consumer version of Skylake-S, which is something discussed and analyzed in this review.

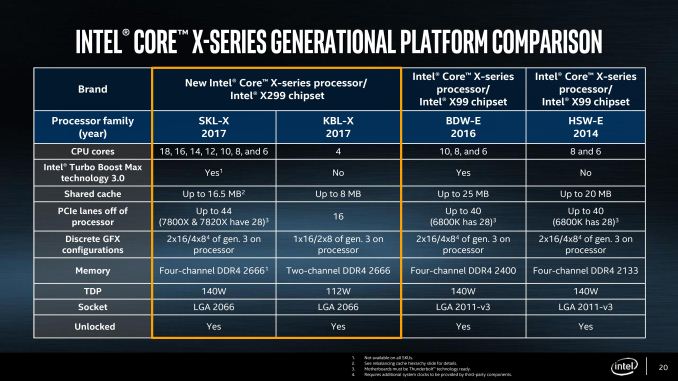

The final element to the Basin Falls launch is Kaby Lake-X. This is also an aspect of the Basin Falls platform that deviates from the previous generations. Intel’s HEDT line has historically been one generation behind the mainstream consumer platform due to enterprise life cycles as well as the added difficulty of producing these larger chips. As a result, the enterprise and HEDT parts have never had the peak processing efficiency (IPC, instructions per clock) of the latest designs and have sat in the wings, waiting. By bringing the Kaby Lake microarchitecture to HEDT, this changes the scene, albeit slightly. Rather than bringing a new big core featuring the latest microarchitecture, Intel is repurposing the Kaby Lake-S mainstream consumer silicon, binning it to slightly more stringent requirements for frequency and power, disabling the integrated graphics, and then putting it in a package for the high-end desktop platform. There are still some significant limitations, such as having only 16 PCIe 3.0 lanes and dual channel memory, which might exclude it from the traditional designation of being a true HEDT processor, however Intel has stated that these parts fill a request from customers to have the latest microarchitecture on the HEDT platform. They also overclock quite well, which is worth noting.

The Kaby Lake-X parts will consist of a Core i7 and Core i5, both of which are quad core parts, with the i7 supporting hyperthreading. We have a parallel Kaby Lake-X review alongside our Skylake-X coverage, with some numbers from a stable 5 GHz overclock.

264 Comments

View All Comments

Tuna-Fish - Tuesday, June 20, 2017 - link

Just a tiny nitpick about the cache hierarchy table:TLBs are grouped with cache levels, that is, L1TLBs are with the L1 caches and the L2 TLB is with the L2 cache, as if the level of TLB is associated with the level of cache. This is not how they work -- any request only has to have it's address translated once, when it's loaded from the L1 cache. If there is a miss when accessing the L1 TLB, the L2 TLB is accessed before the L1 cache is.

PeterCordes - Monday, July 3, 2017 - link

This common mistake bugs me too! The transistors for the TLB's 2nd level are probably not even near the L2 cache. (And the L2 cache is physically indexed / physically tagged, so it doesn't care about translations or virtual addresses at all). The multi-level TLB is a separate hierarchy from the normal caches.I also commented earlier to point out several other errors in [the uarch details](http://www.anandtech.com/comments/11550/the-intel-... e.g. mixing up the register-file sizes with the scheduler size.

yeeeeman - Tuesday, June 20, 2017 - link

What this review shows just how good of a deal AMD Ryzen CPUs are. I mean, R7 1700 is like 300$ and it keeps up in many of the tests with the big boys from Intel.Carmen00 - Tuesday, June 20, 2017 - link

Small typo on the first page, Ian: "For $60 less than the price of the Core i7-7800X...". But the comparison shows $389 vs $299, which is a $90 difference. Otherwise a fantastic, in-depth review, thank you very much!Ian Cutress - Tuesday, June 20, 2017 - link

Official MSRPs haven't changed. What distributors do with their stock is a different story.Carmen00 - Wednesday, June 21, 2017 - link

I'm talking about the MSRPs. There's a table ("Comparison: Core i7-7800X vs. Ryzen 7 1700") on Page 1 with the MSRPs as $299 and $389, a $90 difference. The text just above this table says that there's a $60 difference, but 389-299=90, not 60. So either the text is incorrect, or the MSRPs in the table are incorrect.Tephereth - Tuesday, June 20, 2017 - link

Missing temps and in-game benchmarks... u're the only one in the whole web that has an 7800x to test, so please post those :(Gothmoth - Tuesday, June 20, 2017 - link

after reading a dozend reviews i say:great now we have the choice between two buggy platforms.... well done.

i am not going to be a bios betatester for AMD or Intel.

these two release are the worst in many years i would say.

i hope AMD has threadripper ironed out.

AntDX316 - Tuesday, June 20, 2017 - link

The new processors are in totally another level/league/class. It dominates in everything and more except a couple benches.AnandTechReader2017 - Tuesday, June 20, 2017 - link

Of course they are, Ryzen is mainstream, Thread Ripper is the competitor.Thread Ripper will be quite interesting, the scaling of the "infinity fabric" will come to the fore and show if AMD's new architecture is a worthy competitor.