AMD Briefly Shows Off Zen “Summit Ridge” Silicon

by Ryan Smith on May 31, 2016 11:15 PM EST- Posted in

- CPUs

- AMD

- Zen

- Computex_2016

- AM4

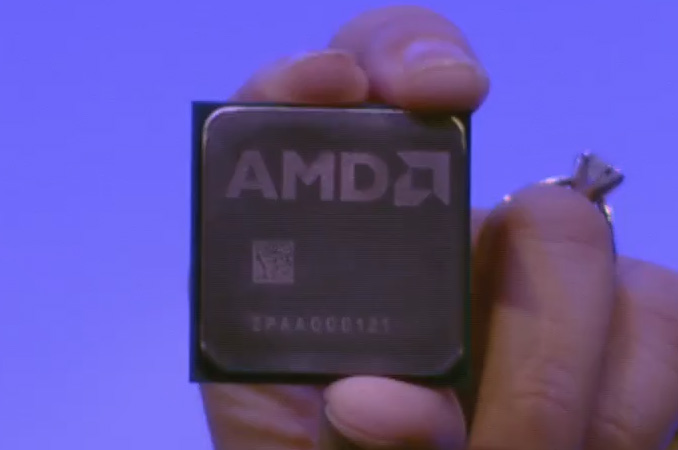

After an already packed Computex 2016 event with Radeon Polaris and Bristol Ridge/Stoney Ridge news, AMD CEO Dr. Lisa Su had one final surprise to close out the company’s presentation: Zen, in the flesh.

Zen taped out earlier this year, and AMD is now working on bringing it up in their labs. To that end Dr. Su pulled out a very early engineering sample of what will be AMD’s Summit Ridge CPU, an 8 core Zen-based CPU. Summit Ridge will use AMD’s new AM4 socket – currently being rolled out for Bristol Ridge – making it a drop-in platform replacement.

Little in the way of new details on Summit Ridge and Zen were released, but Dr. Su confirmed that AMD is still targeting a 40% IPC increase. On the development front, the chip still has some work to undergo, but AMD is to the point where they are going to start sampling their top-tier, high profile customers with engineering samples here in a few weeks. Wider sampling to their larger OEM base will in turn take place in Q3 of this year. AMD has not mentioned a retail product date, but keep in mind there’s a fairly significant lag time between OEM sampling and retail products.

Finally, Dr. Su also reiterated that Zen will be the basis of a range of products for AMD. Along with the desktop CPU, AMD will be using Zen as the basis of their next, 8th generation APU. And further down the line it will be appearing in server products and embedded products as well.

89 Comments

View All Comments

utroz - Sunday, June 5, 2016 - link

BTW no current AMD apu's have L3 cache including Bristol Ridge. Bristol Ridge high end APU's have 2MB of L2.http://www.amd.com/en-us/products/processors/lapto... Go down to "Model Comparisons and Specs" and it will show details for the APU's..

MobiusPizza - Thursday, June 9, 2016 - link

AMD doesn't have the process node technology nor the fabrication production capability to brute force that much cache on a chip and still remain price competitive with Intel. The smaller cache is why AMD can still survive despite selling chips half the price of intel for so long.MobiusPizza - Thursday, June 9, 2016 - link

AMD doesn't have the process node technology nor the fabrication production capability to brute force that much cache on a chip and still remain price competitive with Intel. The smaller cache is why AMD can still survive despite selling chips half the price of intel for so long.killerbunnies - Wednesday, June 1, 2016 - link

With a 40% IPC increase, it is still looking way up to Skylake i7 desktop platforms.B3an - Wednesday, June 1, 2016 - link

If Zen actually has 8 *REAL* cores this time, then it could be faster at highly multi-threaded tasks. It will never beat Broadwell-E, but Skylake which only has 4 cores (still! pathetic) could be beaten by Zen.BTW, does anyone know if they're real fully individual cores in Zen? None of that shared core crap like their previous CPUs, which AMD are rightly being sued over for false advertising.

Arnulf - Wednesday, June 1, 2016 - link

Yes, they are full cores with SMT, very much like Intel's cores.8 core Zen chip means 16 threads.

AS118 - Wednesday, June 1, 2016 - link

Which is good, and I hear they'll have 6-cores with 12 threads too. Which I may end up buying, because if the 8-core is really that good, they'll price it accordingly. So I may have to get a 6-core Zen if/when I upgrade.davegraham - Wednesday, June 1, 2016 - link

no, 4c/8t; 8c/16t will be the APU low-end. each set of cores is built into a 4 core module. so, your multipliers for cores will be in blocks of 4.each core will have 512k of L2 with a minimum of 2mb of L3 per block of 4 cores. (last time i checked)

subject to change, as it were.

looncraz - Wednesday, June 1, 2016 - link

There is no reason AMD can't disable one, two, or even three cores within a module - the cores only share L3 and an inter-core bus. You can leave one core in a module enabled and disable the other three, leaving that one core with all of the L3... or you can even slice off part of the L3.So the Summit Ridge die could be configured with any of the following core configurations:

1, 2, 3, 4, 5, 6, 7, 8

And SMT can be disabled as well...

Of course, AMD will probably only offer six and eight core designs as that should equate to 90%+ effective yields while still commanding good margin and market penetration. An up-charge for SMT would allow them to address even more of the market with the same die.

lunchbox4k - Wednesday, June 1, 2016 - link

I cant wait to see. If I get my facts right. AMD moved from SMC using 4 sections containing two integer clusters and a sharable FPU cluster only able to execute one thread per integer cluster; to SMT with 8 modules containing one integer and FPU cluster with the ability to process multiple threads each (In Intel and presumably AMD's case two threads are interlaced). This is a major gain, so who knows. I remember a company with a product with 8 cores later adding two more in light of news from the competitor.